| Revision as of 10:27, 22 April 2007 editVVVBot (talk | contribs)8,665 editsm robot Adding: pl:Adres fizyczny← Previous edit | Revision as of 19:52, 31 May 2007 edit undoFabartus (talk | contribs)Extended confirmed users21,651 edits Maj expansion -- how in the heck did this get neglected so long!Next edit → | ||

| Line 1: | Line 1: | ||

| In |

In computers, a '''physical address''' or '''binary address''' is the value of the ] monotonically ordered ] ] presented on the ]'s ] control structure called an ] which is used electronically by the circuitry to directly enable a ''particular memory storage cell'' (itself part of the circuitry) using other boolean logic circuitry, the Memory Management Unit (MMU). | ||

| ⚫ | In network connection, physical address also means ]. | ||

| ] | ] | ||

| In essense, any address (virtual or physical) is a coded command to (or from) the memory decoder logic (MMU) selecting exactly one memory cell of fixed width called a "word" or "data word" particular to the computers design, though in data retrieval contexts, the term may also refer to a part of one such word such as a byte or half word size given the particulars of a specific computer design. | |||

| Once 'just' called an '''Address''' (or ''the Address'') until the advent of virtual addressing schemes and paged memory blocks required further distinctions— each memory data location in both ] and ] memory types holds a generic ] ''of some sort'' usually referred to as a 'code' (or coded data, because how it's interpreted, its type and meaning and use all depend on the context of the instructions which retrieve and manipulate it) and each such coded data item has a unique physically determined position which is enabled by another unique binary number, '''the address''', of that single data word, much like each house on a street has a unique number along a street. | |||

| Each data address contains a binary word sized characteristic to the design of the computers' ] (CPU) which in practice has historically been sized in multiples of four and eight bit chunks (''nibbles'' and ''bytes'' respectively) so that at one time or another computer words of four, eight, twelve, sixteen, twenty-four, thirty-two, fourty-eight, sixty-four (and larger) came into vouge with advances in processing and memory architecture. Each memory location (address) may contain either coded instructions, or binary data (text data, binary numeric data and so forth) the common fact being they are all just numbers that fit within the word size of the machine storing them. How they are interpreted and used is determined by the context of the retrieving instruction code (]) currently in control of the MPU and how they are combined with other elements of such coded data by the software. | |||

| Instructions in an storage address are contextually interpreted as command words to the systems main processing unit, and data is retrieved by such instructions placed in an internal and isolated memory structure called a ], where the next (or some subsequent) instruction can manipulate it in conjunction with data retrieved into other internal memory locations (or '''internal addresses'''). Registers are the memory addresses within the part of the central processing unit known as the ] (ALU), which responds to ]s (Machine code) fetched into instruction registers selecting combinatorial logic determining which ]s should be added, subtracted, circulated (shifted) and so forth at the ground level (]) of binary manipulation of data. | |||

| In more modern systems using memory mapping and paging which came into widespread use in personal computers in the later part of the 80's, aliasing and swapping within the physical addressing binary limits creating a requirement for a ] handling system when the technique is employed. Prior to personal computers, virtual memory handling and swapping was common in time sharing main frame computers and other multi-user types of computing systems sharing computing time in different tasking. In personal computers, the virtual memory technique was first employed to expand the finite computer address space (at that time fixed at 640 contiguous ] by the architecture of the original ]'s locating video memory starting in that address and above) into the ability to use memory pages at physical addresses above the video ram addresses range which enabled the physically determined (by microprocessor type) upper memory limitations of one megabyte to be fully utilized. Shortly afterwards, paging schemes and MMU addons enabled the upper physical memory limit of one megabyte to be exceeded further increasing the capabilities of such systems. Despite advances in ] designs and personal computer architecture since, which enable much larger physical memory limits to be used, the ancient design holdover of placement of video memory in the middle of the first megabyte of physical address space still continues the need for exotic handling of memory management in all IBM PC descended computer systems forcing a resort to use of a ] scheme and MMU indexed by the binary address generated by the ] relative to some block (memory page) of organized contiquous memory. Such ]es are translated into '''physical addresses''' by a ] (abbreviated MMU) which must also be commanded by the processor and software which block is "current" for a range of addresses. This is a somewhat cumbersome and inefficient arrangement in comparison to an architecture (like the Apple ] which does not need to resort to the necessary overhead and occasional delays as blocks of data are swapped to hard disk and so forth. | |||

| ⚫ | In network connection, physical address also means ]. | ||

| '''See Also:''' | '''See Also:''' | ||

| Line 8: | Line 19: | ||

| * ] | * ] | ||

| ] and ] | |||

| ] | ] | ||

Revision as of 19:52, 31 May 2007

In computers, a physical address or binary address is the value of the finite monotonically ordered binary number presented on the computer's main memory control structure called an computer address buss which is used electronically by the circuitry to directly enable a particular memory storage cell (itself part of the circuitry) using other boolean logic circuitry, the Memory Management Unit (MMU).

In essense, any address (virtual or physical) is a coded command to (or from) the memory decoder logic (MMU) selecting exactly one memory cell of fixed width called a "word" or "data word" particular to the computers design, though in data retrieval contexts, the term may also refer to a part of one such word such as a byte or half word size given the particulars of a specific computer design.

Once 'just' called an Address (or the Address) until the advent of virtual addressing schemes and paged memory blocks required further distinctions— each memory data location in both ROM and RAM memory types holds a generic binary number of some sort usually referred to as a 'code' (or coded data, because how it's interpreted, its type and meaning and use all depend on the context of the instructions which retrieve and manipulate it) and each such coded data item has a unique physically determined position which is enabled by another unique binary number, the address, of that single data word, much like each house on a street has a unique number along a street.

Each data address contains a binary word sized characteristic to the design of the computers' central processing unit (CPU) which in practice has historically been sized in multiples of four and eight bit chunks (nibbles and bytes respectively) so that at one time or another computer words of four, eight, twelve, sixteen, twenty-four, thirty-two, fourty-eight, sixty-four (and larger) came into vouge with advances in processing and memory architecture. Each memory location (address) may contain either coded instructions, or binary data (text data, binary numeric data and so forth) the common fact being they are all just numbers that fit within the word size of the machine storing them. How they are interpreted and used is determined by the context of the retrieving instruction code (computer software) currently in control of the MPU and how they are combined with other elements of such coded data by the software.

Instructions in an storage address are contextually interpreted as command words to the systems main processing unit, and data is retrieved by such instructions placed in an internal and isolated memory structure called a storage register, where the next (or some subsequent) instruction can manipulate it in conjunction with data retrieved into other internal memory locations (or internal addresses). Registers are the memory addresses within the part of the central processing unit known as the Arithmetic Logic Unit (ALU), which responds to binary instructions (Machine code) fetched into instruction registers selecting combinatorial logic determining which data registers should be added, subtracted, circulated (shifted) and so forth at the ground level (Machine language) of binary manipulation of data.

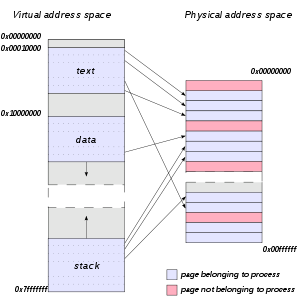

In more modern systems using memory mapping and paging which came into widespread use in personal computers in the later part of the 80's, aliasing and swapping within the physical addressing binary limits creating a requirement for a virtual memory handling system when the technique is employed. Prior to personal computers, virtual memory handling and swapping was common in time sharing main frame computers and other multi-user types of computing systems sharing computing time in different tasking. In personal computers, the virtual memory technique was first employed to expand the finite computer address space (at that time fixed at 640 contiguous kilobytes by the architecture of the original IBM PC's locating video memory starting in that address and above) into the ability to use memory pages at physical addresses above the video ram addresses range which enabled the physically determined (by microprocessor type) upper memory limitations of one megabyte to be fully utilized. Shortly afterwards, paging schemes and MMU addons enabled the upper physical memory limit of one megabyte to be exceeded further increasing the capabilities of such systems. Despite advances in microprocessor designs and personal computer architecture since, which enable much larger physical memory limits to be used, the ancient design holdover of placement of video memory in the middle of the first megabyte of physical address space still continues the need for exotic handling of memory management in all IBM PC descended computer systems forcing a resort to use of a virtual address scheme and MMU indexed by the binary address generated by the CPU relative to some block (memory page) of organized contiquous memory. Such Virtual addresses are translated into physical addresses by a memory management unit (abbreviated MMU) which must also be commanded by the processor and software which block is "current" for a range of addresses. This is a somewhat cumbersome and inefficient arrangement in comparison to an architecture (like the Apple MacIntosh which does not need to resort to the necessary overhead and occasional delays as blocks of data are swapped to hard disk and so forth.

In network connection, physical address also means MAC address.

See Also:

computer engineering and computer science

This computer science article is a stub. You can help Misplaced Pages by expanding it. |