Phase-change memory (also known as PCM, PCME, PRAM, PCRAM, OUM (ovonic unified memory) and C-RAM or CRAM (chalcogenide RAM)) is a type of non-volatile random-access memory. PRAMs exploit the unique behaviour of chalcogenide glass. In PCM, heat produced by the passage of an electric current through a heating element generally made of titanium nitride is used to either quickly heat and quench the glass, making it amorphous, or to hold it in its crystallization temperature range for some time, thereby switching it to a crystalline state. PCM also has the ability to achieve a number of distinct intermediary states, thereby having the ability to hold multiple bits in a single cell, but the difficulties in programming cells in this way has prevented these capabilities from being implemented in other technologies (most notably flash memory) with the same capability.

Recent research on PCM has been directed towards attempting to find viable material alternatives to the phase-change material Ge2Sb2Te5 (GST), with mixed success. Other research has focused on the development of a GeTe–Sb2Te3 superlattice to achieve non-thermal phase changes by changing the co-ordination state of the germanium atoms with a laser pulse. This new Interfacial Phase-Change Memory (IPCM) has had many successes and continues to be the site of much active research.

Leon Chua has argued that all two-terminal non-volatile-memory devices, including PCM, should be considered memristors. Stan Williams of HP Labs has also argued that PCM should be considered a memristor. However, this terminology has been challenged, and the potential applicability of memristor theory to any physically realizable device is open to question.

Background

In the 1960s, Stanford R. Ovshinsky of Energy Conversion Devices first explored the properties of chalcogenide glasses as a potential memory technology. In 1969, Charles Sie published a dissertation at Iowa State University that both described and demonstrated the feasibility of a phase-change-memory device by integrating chalcogenide film with a diode array. A cinematographic study in 1970 established that the phase-change-memory mechanism in chalcogenide glass involves electric-field-induced crystalline filament growth. In the September 1970 issue of Electronics, Gordon Moore, co-founder of Intel, published an article on the technology. However, material quality and power consumption issues prevented commercialization of the technology. More recently, interest and research have resumed as flash and DRAM memory technologies are expected to encounter scaling difficulties as chip lithography shrinks.

The crystalline and amorphous states of chalcogenide glass have dramatically different electrical resistivity values. The amorphous, high resistance state represents a binary 0, while the crystalline, low resistance state represents a 1. Chalcogenide is the same material used in re-writable optical media (such as CD-RW and DVD-RW). In those instances, the material's optical properties are manipulated, rather than its electrical resistivity, as chalcogenide's refractive index also changes with the state of the material.

Although PRAM has not yet reached the commercialization stage for consumer electronic devices, nearly all prototype devices make use of a chalcogenide alloy of germanium (Ge), antimony (Sb) and tellurium (Te) called GeSbTe (GST). The stoichiometry, or Ge:Sb:Te element ratio, is 2:2:5 in GST. When GST is heated to a high temperature (over 600 °C), its chalcogenide crystallinity is lost. Once cooled, it is frozen into an amorphous glass-like state and its electrical resistance is high. By heating the chalcogenide to a temperature above its crystallization point, but below the melting point, it will transform into a crystalline state with a much lower resistance. The time to complete this phase transition is temperature-dependent. Cooler portions of the chalcogenide take longer to crystallize, and overheated portions may be remelted. A crystallization time scale on the order of 100 ns is commonly used. This is longer than conventional volatile memory devices like modern DRAM, which have a switching time on the order of two nanoseconds. However, a January 2006 Samsung Electronics patent application indicates PRAM may achieve switching times as fast as five nanoseconds.

A 2008 advance pioneered by Intel and ST Microelectronics allowed the material state to be more carefully controlled, allowing it to be transformed into one of four distinct states: the previous amorphous or crystalline states, along with two new partially crystalline ones. Each of these states has different electrical properties that can be measured during reads, allowing a single cell to represent two bits, doubling memory density.

Aluminum/antimony

Phase-change memory devices based on germanium, antimony and tellurium present manufacturing challenges, since etching and polishing of the material with chalcogens can change the material's composition. Materials based on aluminum and antimony are more thermally stable than GeSbTe. Al50Sb50 has three distinct resistance levels, offering the potential to store three bits of data in two cells as opposed to two (nine states possible for the pair of cells, using eight of those states yields log2 8 = 3 bits).

PRAM vs. Flash

PRAM's switching time and inherent scalability make it more appealing than flash memory. PRAM's temperature sensitivity is perhaps its most notable drawback, one that may require changes in the production process of manufacturers incorporating the technology.

Flash memory works by modulating charge (electrons) stored within the gate of a MOS transistor. The gate is constructed with a special "stack" designed to trap charges (either on a floating gate or in insulator "traps"). The presence of charge within the gate shifts the transistor's threshold voltage higher or lower, corresponding to a change in the cell's bit state from 1 to 0 or 0 to 1. Changing the bit's state requires removing the accumulated charge, which demands a relatively large voltage to "suck" the electrons off the floating gate. This burst of voltage is provided by a charge pump, which takes some time to build up power. General write times for common flash devices are on the order of 100 μs (for a block of data), about 10,000 times the typical 10 ns read time for SRAM for example (for a byte).

PRAM can offer much higher performance in applications where writing quickly is important, both because the memory element can be switched more quickly, and also because single bits may be changed to either 1 or 0 without needing to first erase an entire block of cells. PRAM's high performance, thousands of times faster than conventional hard drives, makes it particularly interesting in nonvolatile memory roles that are currently performance-limited by memory access timing.

In addition, with flash, each burst of voltage across the cell causes degradation. As the size of the cells decreases, damage from programming grows worse because the voltage necessary to program the device does not scale with the lithography. Most flash devices are rated for, currently, only 5,000 writes per sector, and many flash controllers perform wear leveling to spread writes across many physical sectors.

PRAM devices also degrade with use, for different reasons than flash, but degrade much more slowly. A PRAM device may endure around 100 million write cycles. PRAM lifetime is limited by mechanisms such as degradation due to GST thermal expansion during programming, metal (and other material) migration, and other mechanisms still unknown.

Flash parts can be programmed before being soldered onto a board, or even purchased pre-programmed. The contents of a PRAM, however, are lost because of the high temperatures needed to solder the device to a board (see reflow soldering or wave soldering). This was made worse by the requirement to have lead-free manufacturing requiring higher soldering temperatures. A manufacturer using PRAM parts must provide a mechanism to program the PRAM "in-system" after it has been soldered in place.

The special gates used in flash memory "leak" charge (electrons) over time, causing corruption and loss of data. The resistivity of the memory element in PRAM is more stable; at the normal working temperature of 85 °C, it is projected to retain data for 300 years.

By carefully modulating the amount of charge stored on the gate, flash devices can store multiple (usually two) bits in each physical cell. In effect, this doubles the memory density, reducing cost. PRAM devices originally stored only a single bit in each cell, but Intel's recent advances have removed this problem.

Because flash devices trap electrons to store information, they are susceptible to data corruption from radiation, making them unsuitable for many space and military applications. PRAM exhibits higher resistance to radiation.

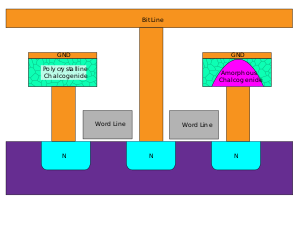

PRAM cell selectors can use various devices: diodes, BJTs and MOSFETs. Using a diode or a BJT provides the greatest amount of current for a given cell size. However, the concern with using a diode stems from parasitic currents to neighboring cells, as well as a higher voltage requirement, resulting in higher power consumption. Chalcogenide resistance is necessarily larger than that of a diode, meaning operating voltage must exceed 1 V by a wide margin to guarantee adequate forward bias current from the diode. Perhaps the most severe consequence of using a diode-selected array, in particular for large arrays, is the total reverse bias leakage current from the unselected bit lines. In transistor-selected arrays, only the selected bit lines contribute reverse bias leakage current. The difference in leakage current is several orders of magnitude. A further concern with scaling below 40 nm is the effect of discrete dopants as the p-n junction width scales down. Thin film-based selectors allow higher densities, utilizing < 4 F cell area by stacking memory layers horizontally or vertically. Often the isolation capabilities are inferior to the use of transistors if the on/off ratio for the selector is not sufficient, limiting the ability to operate very large arrays in this architecture. Chalcogenide-based threshold switches have been demonstrated as a viable selector for high-density PCM arrays

2000 and later

In August 2004, Nanochip licensed PRAM technology for use in MEMS (micro-electric-mechanical-systems) probe storage devices. These devices are not solid state. Instead, a very small platter coated in chalcogenide is dragged beneath thousands or even millions of electrical probes that can read and write the chalcogenide. Hewlett-Packard's micro-mover technology can accurately position the platter to 3 nm so densities of more than 1 Tbit (125 GB) per square inch will be possible if the technology can be perfected. The basic idea is to reduce the amount of wiring needed on-chip; instead of wiring every cell, the cells are placed closer together and read by current passing through the MEMS probes, acting like wires. This approach resembles IBM's Millipede technology.

Samsung 46.7 nm cell

In September 2006, Samsung announced a prototype 512 Mb (64 MB) device using diode switches. The announcement was something of a surprise, and it was especially notable for its fairly high memory density. The prototype featured a cell size of only 46.7 nm, smaller than commercial flash devices available at the time. Although flash devices of higher capacity were available (64 Gb, or 8 GB, was just coming to market), other technologies competing to replace flash in general offered lower densities (larger cell sizes). The only production MRAM and FeRAM devices are only 4 Mb, for example. The high density of Samsung's prototype PRAM device suggested it could be a viable flash competitor, and not limited to niche roles as other devices have been. PRAM appeared to be particularly attractive as a potential replacement for NOR flash, where device capacities typically lag behind those of NAND flash devices. State-of-the-art capacities on NAND passed 512 Mb some time ago. NOR flash offers similar densities to Samsung's PRAM prototype and already offers bit addressability (unlike NAND where memory is accessed in banks of many bytes at a time).

Intel's PRAM device

Samsung's announcement was followed by one from Intel and STMicroelectronics, who demonstrated their own PRAM devices at the 2006 Intel Developer Forum in October. They showed a 128 Mb part that began manufacture at STMicroelectronics's research lab in Agrate, Italy. Intel stated that the devices were strictly proof-of-concept.

BAE device

PRAM is also a promising technology in the military and aerospace industries where radiation effects make the use of standard non-volatile memories such as flash impractical. PRAM devices have been introduced by BAE Systems, referred to as C-RAM, claiming excellent radiation tolerance (rad-hard) and latchup immunity. In addition, BAE claims a write cycle endurance of 10, which will allow it to be a contender for replacing PROMs and EEPROMs in space systems.

Multi-level cell

In February 2008, Intel and STMicroelectronics revealed the first multilevel (MLC) PRAM array prototype. The prototype stored two logical bits in each physical cell, in effect 256 Mb of memory stored in a 128 Mb physical array. This means that instead of the normal two states—fully amorphous and fully crystalline—an additional two distinct intermediate states represent different degrees of partial crystallization, allowing for twice as many bits to be stored in the same physical area. In June 2011, IBM announced that they had created stable, reliable, multi-bit phase-change memory with high performance and stability. SK Hynix had a joint developmental agreement and a technology license agreement with IBM for the development of multi-level PRAM technology.

Intel's 90 nm device

Also in February 2008, Intel and STMicroelectronics shipped prototype samples of their first PRAM product to customers. The 90 nm, 128 Mb (16 MB) product was called Alverstone.

In June 2009, Samsung and Numonyx B.V. announced a collaborative effort in the development of PRAM market-tailored hardware products.

In April 2010, Numonyx announced the Omneo line of 128-Mbit NOR-compatible phase-change memories. Samsung announced shipment of 512 Mb phase-change RAM (PRAM) in a multi-chip package (MCP) for use in mobile handsets by Fall 2010.

ST 28 nm, 16 MB array

In December 2018 STMicroelectronics presented design and performance data for a 16 MB ePCM array for a 28 nm fully depleted silicon on insulator automotive control unit.

In-memory computing

More recently, there is significant interest in the application of PCM for in-memory computing. The essential idea is to perform computational tasks such as matrix-vector-multiply operations in the memory array itself by exploiting PCM's analog storage capability and Kirchhoff's circuit laws. PCM-based in-memory computing could be interesting for applications such as deep learning inference which do not require very high computing precision. In 2021, IBM published a full-fledged in-memory computing core based on multi-level PCM integrated in 14 nm CMOS technology node.

Challenges

The greatest challenge for phase-change memory has been the requirement of high programming current density (>10 A/cm, compared to 10...10 A/cm for a typical transistor or diode). The contact between the hot phase-change region and the adjacent dielectric is another fundamental concern. The dielectric may begin to leak current at higher temperature, or may lose adhesion when expanding at a different rate from the phase-change material.

Phase-change memory is susceptible to a fundamental tradeoff of unintended vs. intended phase-change. This stems primarily from the fact that phase-change is a thermally driven process rather than an electronic process. Thermal conditions that allow for fast crystallization should not be too similar to standby conditions, e.g. room temperature, otherwise data retention cannot be sustained. With the proper activation energy for crystallization it is possible to have fast crystallization at programming conditions while having very slow crystallization at normal conditions.

Probably the biggest challenge for phase-change memory is its long-term resistance and threshold voltage drift. The resistance of the amorphous state slowly increases according to a power law (~t). This severely limits the ability for multilevel operation, since a lower intermediate state would be confused with a higher intermediate state at a later time, and could also jeopardize standard two-state operation if the threshold voltage increases beyond the design value.

In April 2010, Numonyx released its Omneo line of parallel and serial interface 128 Mb NOR flash replacement PRAM chips. Although the NOR flash chips they intended to replace operated in the −40-85 °C range, the PRAM chips operated in the 0-70 °C range, indicating a smaller operating window compared to NOR flash. This is likely due to the use of highly temperature-sensitive p–n junctions to provide the high currents needed for programming.

Timeline

- January 1955: Kolomiets and Gorunova revealed semiconducting properties of chalcogenide glasses.

- September 1966: Stanford Ovshinsky files first patent on phase-change technology

- January 1969: Charles H. Sie published a dissertation at Iowa State University on chalcogenide phase-change-memory device

- June 1969: US Patent 3,448,302 (Shanefield) licensed to Ovshinsky claims first reliable operation of PRAM device

- September 1970: Gordon Moore publishes research in Electronics Magazine

- June 1999: Ovonyx joint venture is formed to commercialize PRAM technology

- November 1999: Lockheed Martin works with Ovonyx on PRAM for space applications

- February 2000: Intel invests in Ovonyx, licenses technology

- December 2000: ST Microelectronics licenses PRAM technology from Ovonyx

- March 2002: Macronix files a patent application for transistor-less PRAM

- July 2003: Samsung begins work on PRAM technology

- 2003 through 2005: PRAM-related patent applications filed by Toshiba, Hitachi, Macronix, Renesas, Elpida, Sony, Matsushita, Mitsubishi, Infineon and more

- August 2004: Nanochip licenses PRAM technology from Ovonyx for use in MEMS probe storage

- August 2004: Samsung announces successful 64 Mbit PRAM array

- February 2005: Elpida licenses PRAM technology from Ovonyx

- September 2005: Samsung announces successful 256 Mbit PRAM array, touts 400 μA programming current

- October 2005: Intel increases investment in Ovonyx

- December 2005; Hitachi and Renesas announce 1.5 V PRAM with 100 μA programming current

- December 2005: Samsung licenses PRAM technology from Ovonyx

- July 2006: BAE Systems begins selling the first commercial PRAM chip

- September 2006: Samsung announces 512 Mbit PRAM device

- October 2006: Intel and STMicroelectronics show a 128 Mbit PRAM chip

- December 2006: IBM Research Labs demonstrate a prototype 3 by 20 nanometers

- January 2007: Qimonda licenses PRAM technology from Ovonyx

- April 2007: Intel's chief technology officer Justin Rattner is set to give the first public demonstration of the company's PRAM (phase-change RAM) technology

- October 2007: Hynix begins pursuing PRAM by licensing Ovonyx' technology

- February 2008: Intel and STMicroelectronics announce four-state MLC PRAM and begin shipping samples to customers.

- December 2008: Numonyx announces mass production 128 Mbit PRAM device to selected customer.

- June 2009: Samsung's phase-change RAM will go into mass production starting in June

- September 2009: Samsung announces mass production start of 512 Mbit PRAM device

- October 2009: Intel and Numonyx announce they have found a way to stack phase-change memory arrays on one die

- December 2009: Numonyx announces 1 Gb 45 nm product

- April 2010: Numonyx releases Omneo PRAM Series (P8P and P5Q), both in 90 nm.

- April 2010: Samsung releases 512 Mbit PRAM with 65 nm process, in Multi-Chip-Package.

- February 2011: Samsung presented 58 nm 1.8V 1 Gb PRAM.

- February 2012: Samsung presented 20 nm 1.8V 8 Gb PRAM

- July 2012: Micron announces availability of Phase-Change Memory for mobile devices - the first PRAM solution in volume production

- January 2014: Micron withdraws all PCM parts from the market.

- May 2014: IBM demonstrates combining PCM, conventional NAND, and DRAM on a single controller

- August 2014: Western Digital demonstrates prototype PCM storage with 3 million I/Os and 1.5 microsecond latency

- July 2015: Intel and Micron announced 3D Xpoint memory where phase-change alloy is used as a storage part of a memory cell.

See also

- Ferroelectric RAM (FRAM)

- Magnetoresistive random-access memory (MRAM)

- Read-mostly memory (RMM)

References

- Le Gallo, Manuel; Sebastian, Abu (2020-03-30). "An overview of phase-change memory device physics". Journal of Physics D: Applied Physics. 53 (21): 213002. Bibcode:2020JPhD...53u3002L. doi:10.1088/1361-6463/ab7794. ISSN 0022-3727. S2CID 213023359.

- Burr, Geoffrey W.; BrightSky, Matthew J.; Sebastian, Abu; Cheng, Huai-Yu; Wu, Jau-Yi; Kim, Sangbum; Sosa, Norma E.; Papandreou, Nikolaos; Lung, Hsiang-Lan; Pozidis, Haralampos; Eleftheriou, Evangelos (June 2016). "Recent Progress in Phase-Change Memory Technology". IEEE Journal on Emerging and Selected Topics in Circuits and Systems. 6 (2): 146–162. Bibcode:2016IJEST...6..146B. doi:10.1109/JETCAS.2016.2547718. ISSN 2156-3357. S2CID 26729693.

- Simpson, R.E.; P. Fons; A. V. Kolobov; T. Fukaya; et al. (July 2011). "Interfacial phase-change memory". Nature Nanotechnology. 6 (8): 501–5. Bibcode:2011NatNa...6..501S. doi:10.1038/nnano.2011.96. PMID 21725305. S2CID 6684244.

- Chua, L. O. (2011), "Resistance switching memories are memristors", Applied Physics A, 102 (4): 765–783, Bibcode:2011ApPhA.102..765C, doi:10.1007/s00339-011-6264-9

- Mellor, Chris (10 October 2011), "HP and Hynix to produce the memristor goods by 2013", The Register, retrieved 2012-03-07

- Meuffels, P.; Soni, R. (2012). "Fundamental Issues and Problems in the Realization of Memristors". arXiv:1207.7319 .

- Di Ventra, Massimiliano; Pershin, Yuriy V. (2013). "On the physical properties of memristive, memcapacitive and meminductive systems". Nanotechnology. 24 (25): 255201. arXiv:1302.7063. Bibcode:2013Nanot..24y5201D. CiteSeerX 10.1.1.745.8657. doi:10.1088/0957-4484/24/25/255201. PMID 23708238. S2CID 14892809.

- Sie, C.H. (1969). Memory cell using bistable resistivity in amorphous As-Te-Ge film. Retrospective Theses and Dissertations (PhD). Iowa State University. 3604 https://lib.dr.iastate.edu/rtd/3604.

- Pohm, A.; Sie, C.; Uttecht, R.; Kao, V.; Agrawal, O. (1970). "Chalcogenide glass bistable resistivity (Ovonic) memories". IEEE Transactions on Magnetics. 6 (3): 592. Bibcode:1970ITM.....6..592P. doi:10.1109/TMAG.1970.1066920.

- "Electric-Field Induced Filament Formation in As-Te-Ge Semiconductor" C.H. Sie, R. Uttecht, H. Stevenson, J. D. Griener and K. Raghavan , Journal of Non-Crystalline Solids, 2, 358–370,1970

- "A Cinematic Study of Mechanisms of Phase Change Memory". YouTube. 2012-06-21. Archived from the original on 2021-12-21. Retrieved 2013-09-17.

- Moore, Gordon E.; Neale, R.G.; Nelson, D.L. (September 28, 1970). "Nonvolatile and reprogramable, the read-mostly memory is here" (PDF). Electronics: 56–60. Archived from the original (PDF) on July 7, 2022. Retrieved April 22, 2022.

- "Is NAND flash memory a dying technology?". Techworld. Retrieved 2010-02-04.

- Caravati, Sebastiano; Bernasconi, Marco; Kühne, Thomas D.; Krack, Matthias; Parrinello, Michele (2007). "Coexistence of tetrahedral- and octahedral-like sites in amorphous phase change materials". Applied Physics Letters. 91 (17): 171906. arXiv:0708.1302. Bibcode:2007ApPhL..91q1906C. doi:10.1063/1.2801626. S2CID 119628572.

- Horii, H.; et al. (2003). "A novel cell technology using N-doped GeSbTe films for phase change RAM". 2003 Symposium on VLSI Technology. Digest of Technical Papers. pp. 177–8. doi:10.1109/VLSIT.2003.1221143. ISBN 4-89114-033-X. S2CID 40051862. 03CH37407.

- ^ Greene, Kate (4 February 2008). "A Memory Breakthrough". Technology Review.

- "Will phase-change memory replace flash memory?". KurzweilAI. Retrieved 2013-09-17.

- Zhou, X.; Wu, L.; Song, Z.; Rao, F.; Ren, K.; Peng, C.; Song, S.; Liu, B.; Xu, L.; Feng, S. (2013). "Phase transition characteristics of Al-Sb phase change materials for phase change memory application". Applied Physics Letters. 103 (7): 072114. Bibcode:2013ApPhL.103g2114Z. doi:10.1063/1.4818662.

- Simpson, R. E. (2010). "Toward the Ultimate Limit of Phase Change in Ge2Sb2Te5". Nano Letters. 10 (2): 414–9. Bibcode:2010NanoL..10..414S. doi:10.1021/nl902777z. PMID 20041706. S2CID 9585187.

- "Intel to Sample Phase Change Memory This Year". Archived from the original on 2007-03-23. Retrieved 2007-06-30.

- Pirovano, A.; Redaelli, A.; Pellizzer, F.; Ottogalli, F.; Tosi, M.; Ielmini, D.; Lacaita, A.L.; Bez, R. (2004). "Reliability study of phase-change nonvolatile memories". IEEE Transactions on Device and Materials Reliability. 4 (3): 422–7. doi:10.1109/TDMR.2004.836724. S2CID 22178768.

- Karpov, I.V.; Kencke, D.; Kau, D.; Tang, S.; Spadini, G. (2010). "Phase Change Memory with Chalcogenide Selector (PCMS): Characteristic Behaviors, Physical Models and Key Material Properties". Symposium G – Materials and Physics for Nonvolatile Memories II. MRS Proceedings. Vol. 1250. Cambridge University Press. pp. G14-01–H07-01. doi:10.1557/PROC-1250-G14-01-H07-01.

- SAMSUNG Introduces the Next Generation of Nonvolatile Memory—PRAM

- "Intel Previews Potential Replacement for Flash". Archived from the original on June 29, 2012.

- "IBM develops 'instantaneous' memory, 100x faster than flash". engadget. 2011-06-30. Retrieved 2011-06-30.

- "SK hynix and IBM Sign Joint Development for PCRAM". SK hynix Newsroom. Retrieved 2022-02-05.

- ^ "Intel, STMicroelectronics Deliver Industry's First Phase Change Memory Prototypes". Numonyx. 2008-02-06. Archived from the original on 2008-06-09. Retrieved 2008-08-15.

- "Samsung Electronics and Numonyx Join Forces on Phase Change Memory". Samsung. 2009-06-23.

- "Samsung to ship MCP with phase-change". EE Times. 2010-04-28. Retrieved 2010-05-03.

- "Phase-Change Memory (PCM) - Technology, Advantages & Applications - STMicroelectronics". www.st.com. Retrieved 2022-07-08.

- Burr, Geoffrey W.; Shelby, Robert M.; Sidler, Severin; di Nolfo, Carmelo; Jang, Junwoo; Boybat, Irem; Shenoy, Rohit S.; Narayanan, Pritish; Virwani, Kumar; Giacometti, Emanuele U.; Kurdi, Bulent N. (November 2015). "Experimental Demonstration and Tolerancing of a Large-Scale Neural Network (165 000 Synapses) Using Phase-Change Memory as the Synaptic Weight Element". IEEE Transactions on Electron Devices. 62 (11): 3498–3507. Bibcode:2015ITED...62.3498B. doi:10.1109/TED.2015.2439635. ISSN 0018-9383. S2CID 5243635.

- Sebastian, Abu; Le Gallo, Manuel; Khaddam-Aljameh, Riduan; Eleftheriou, Evangelos (July 2020). "Memory devices and applications for in-memory computing". Nature Nanotechnology. 15 (7): 529–544. Bibcode:2020NatNa..15..529S. doi:10.1038/s41565-020-0655-z. ISSN 1748-3395. PMID 32231270. S2CID 214704544.

- Khaddam-Aljameh, Riduan; Stanisavljevic, Milos; Mas, Jordi Fornt; Karunaratne, Geethan; Brändli, Matthias; Liu, Feng; Singh, Abhairaj; Müller, Silvia M.; Egger, Urs; Petropoulos, Anastasios; Antonakopoulos, Theodore (2022). "HERMES-Core–A 1.59-TOPS/mm² PCM on 14-nm CMOS In-Memory Compute Core Using 300-ps/LSB Linearized CCO-Based ADCs". IEEE Journal of Solid-State Circuits. 57 (4): 1027–1038. Bibcode:2022IJSSC..57.1027K. doi:10.1109/JSSC.2022.3140414. ISSN 1558-173X. S2CID 246417395.

- Karpov, I.V.; Mitra, M.; Kau, D.; Spadini, G.; Kryukov, Y.A.; Karpov, V.G. (2007). "Fundamental drift of parameters in chalcogenide phase change memory". J. Appl. Phys. 102 (12): 124503–124503–6. Bibcode:2007JAP...102l4503K. doi:10.1063/1.2825650.

- Kolomiets, B. T. (1964). "Vitreous Semiconductors (I)". Physica Status Solidi B. 7 (2): 359–372. Bibcode:1964PSSBR...7..359K. doi:10.1002/pssb.19640070202. S2CID 222432031.

- Kolomiets, B. T. (1964). "Vitreous Semiconductors (II)". Physica Status Solidi B. 7 (3): 713–731. Bibcode:1964PSSBR...7..713K. doi:10.1002/pssb.19640070302.

- "Phase Change to Replace Flash?". Archived from the original on September 27, 2007.

- "IT news, careers, business technology, reviews". Computerworld.

- Engadget Samsung PRAM chips go into mass production

- "Samsung moves phase-change memory to production".

- "Intel and Numonyx Achieve Research Milestone with Stacked, Cross Point Phase Change Memory Technology". www.intel.com.

- Numonyx to Present Phase-Change Memory Research Results at Leading Technology Industry Conference

- "Numonyx Memory Solutions - Numonyx Introduces New Phase Change Memory Devices". April 25, 2010. Archived from the original on 25 April 2010.

- "Page Not Found - SAMSUNG". Samsung Electronics America. Archived from the original on August 21, 2010.

{{cite web}}: Cite uses generic title (help) - Chung, H.; et al. (2011). "A 58nm 1.8V 1 Gb PRAM with 6.4 MB/s program BW". 2011 IEEE International Solid-State Circuits Conference. pp. 500–2. doi:10.1109/ISSCC.2011.5746415. ISBN 978-1-61284-303-2. S2CID 206996875.

- A 20nm 1.8V 8Gb PRAM with 40MB/s Program Bandwidth Archived 2012-01-31 at the Wayback Machine

- Micron Announces Availability of Phase Change Memory for Mobile Devices

- Mellor, Chris (14 January 2014). "Micron: Hot DRAM. We don't need no steenkin' PCM". www.theregister.co.uk. The Register. Retrieved 14 January 2014.

- Hruska, Joel (8 May 2014). "IBM demonstrates next-gen phase-change memory that's up to 275 times faster than your SSD". ExtremeTech.

- Hruska, Joel (6 August 2014). "Western Digital's HGST division creates new phase-change SSD that's orders of magnitude faster than any NAND flash drive on the market". ExtremeTech.

External links

- Micron

- Ovonyx, Inc.

- Energy Conversion Devices, Inc.

- Hitachi/Renesas Low-Power PRAM

- Hewlett-Packard Probe Storage

- European\Phase Change and Ovonics Symposium

- BAE C-RAM Radiation-Hardened NVM press release

- BAE C-RAM Radiation-Hardened NVM data sheet

- Introduction to PCM by Numonyx (video)

higher or lower, corresponding to a change in the cell's

higher or lower, corresponding to a change in the cell's