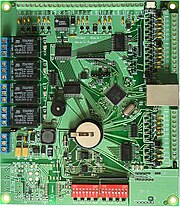

TopoR (Topological Router) is an EDA program developed and maintained by the Russian company Eremex. It is dedicated to laying out a printed circuit board (PCB). The current version is 6.3.17875 as of 2017-09-20.

It features an autorouter and a set of tools intended to reduce the amount of effort needed for manual routing of a PCB. A distinctive feature of TopoR is the absence of preferred routing directions.

History

Work on a flexible topological router began in 1988.

1996 saw the release of the first version of a topological router that actually came to be used by industrial enterprises. In 2002, the FreeStyle Router (FSR) by Диал Инжиниринг ("Dial Engineering") ran under DOS and successfully routed dual-layer boards, interfacing with P-CAD. This early router showed the advantages of an innovative approach to routing and high efficiency of the models, algorithms, and software implementation. A 1.44 MB floppy disk was enough for the program and accompanying examples. The company also announced plans to commercially release a FreeStyle Suite for Windows later the year. The last version of FSR for DOS, consisting of the router named SpeedWay and the layout editor named FreeStyle was version 1.6 as of 2003-09-26/2003-11-01.

The first Windows version of the topological router was released in 2001 and renamed to TopoR. TopoR 1.03 was available on 2003-09-26 and distributed through ElekTrade (ЭлекТрейд). The program routed not only dual-layer but also multi-layer printed circuit boards. TopoR was developed by a group called the FreeStyleTeam, supervised by Sergey J. Luzin (Сергей Юрьевич Лузин), with Oleg B. Polubasov (Олег Борисович Полубасов) as initial FSR developer, as well as Pavel I. Dmitriev (Павел Иванович Дмитриев), Gevorg S. Petrosyan (Геворг Самвелович Петросян), Michael S. Luzin (Михаил Сергеевич Лузин) and Andrew A. Lysenko (Андрей Александрович Лысенко). Version 3.0 was released in 2006. The software was commercially distributed by Prosoft Spb. (ПРОСОФТ СПб) in 2007. TopoR 4.0 added support to import/export DSN design and SES session files. Since TopoR 4.1 (2008) the software is further developed and maintained by Eremex, Ltd.

Features

TopoR can be used as an external autorouter for third-party layout editors or in conjunction with Eremex's own schematic capture and layout editor Delta Design (DD). TopoR imports input in Delta Design's FST format, as Specctra-/ELECTRA-compatible DSN design files, or in P-CAD PCB ASCII (2000, 2002, 2004), PADS PCB ASCII (3.5, 4.0, 5.0, 2005.0), or EAGLE BRD XML formats (6.x). The resulting boards can be exported into Specctra/ELECTRA SES session files, DXF, Gerber, P-CAD PCB ASCII (2000, 2002, 2004), PADS PCB ASCII (3.5, 4.0, 5.0, 2005.0).

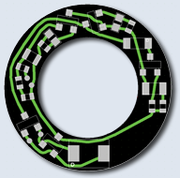

Routing of the wiring topology is done automatically and flexibly; angles are not limited to 90° and 45°.

Efficient use of PCB space and absence of preferred routing directions in layers considerably reduces electromagnetic crosstalk.

TopoR routes all connections, even if this entails violating design constraints. Such violations can be automatically corrected later.

When objects (such as components and vias) are moved around, wire length and shape are optimized automatically with appropriate clearance.

The user is free to choose from two ways to calculate the wire shape: with or without arcs. The first method involves wires consisting of lines only. The other makes wires keep appropriate clearance when circling around pads; it consists of arcs and lines.

TopoR simultaneously optimizes several alternative variants of the layout. Variants with the worst parameters (per total wire length and number of vias) will be removed.

TopoR has an automatic component placement feature. The procedure can be used both for all components of the board and only for components in a specific area. It is not comparable to the quality of the manual placement, but it can be used as a preparation step for manual placement.

The minimum and desired clearances for each net can be specified.

TopoR automatically supports trace necking, that is, it reduces the width of a wire that approaches a narrow pad (or one with a diameter that is less than the width of the wire), or when it passes through bottlenecks (for example, between the pads of a component).

Wire-to-pad transitions use teardrop-style smoothing. The use of this procedure at the design stage helps avoid violations in design-rule checking when teardrops are added in the CAM editor.

TopoR can recognize ball grid array (BGA) component areas and apply a special strategy for routing them. This helps reduce the number of vias, the density of connections, and in some cases the number of routing layers.

A special algorithm is used for routing single-layer boards minimizing the number of interlayer junctions or to find a single-layer routing.

Similar solutions

The layout program PCB of the gEDA suite includes a similar topological autorouter named Toporouter, which was written by Anthony Blake in a Google-funded open source project mentored by DJ Delorie in 2008. It is mostly based on an implementation of the algorithms described in Tal Dayan's 1997 PhD thesis, "Rubberband based topological router". This router has meanwhile been adapted for use with the open-source KiCad project as well.

See also

Notes

- In Russian (the mother language of the developers), topor means "axe".

References

- Обновление версии TopoR 6.3.17875 (in Russian). Eremex. 2017-09-20. Archived from the original on 2017-09-24. Retrieved 2017-09-24.

- Базилевич, Р. П. (1981). Декомпозиционные и топологические методы автоматизированного метода конструирования электронных устройств [Decomposition and topological methods of the automated method of designing electronic devices] (in Russian). Lviv (Львов): Вища школа. p. 168.

- Лузин , Юрьевич Сергей ; Полубасов , Олег Борисович (1997). Пакет гибкой трассировки "FreeStyle Route" [A package of flexible routing "FreeStyle Route"] (in Russian). Odessa: Мат-лы междунар. науч.-техн. конф. "Системы и средства передачи и обработки информации" . p. 35.

- Лузин , Юрьевич Сергей ; Полубасов , Олег Борисович (1997). Трассировка печатных плат - Новые методы решения старых проблем [Routing of printed circuit boards - New methods for solving old problems]. САПР и графика (in Russian) (11): 58–59.

- ^ Сухарев , А. В. (1999). FreeStyleRoute - Трассировка печатных плат [FreeStyleRoute - PCB routing] (in Russian). St. Petersburg, Russia. Archived from the original on 2017-09-25. Retrieved 2017-09-25.

- Бесплатный трассировщик от "Диал". Computerworld Россия (in Russian). 2002 (8). 2002-03-05. Archived from the original on 2017-09-25. Retrieved 2017-09-25.

- ^ Razevig , Vsevolod (2002-03-26). Трассировщик FreeStyle Router доступен в Интернете [FreeStyle Router is available on the Internet]. PC Week/RE / IT week (in Russian). 2002 (11 #329). Archived from the original on 2017-09-25. Retrieved 2017-09-25.

The company Dial Engineering freely offers on the Internet (www.dial-eng.spb.ru) a gridless PCB router FreeStyle Router for DOS and announced the continuation of the development of a FreeStyle CAD Suite for Windows (the commercial release is planned for 2002). If the DOS version only routes single- and double-layer printed circuit boards, the version for Windows is designed to route multi-layer boards. A distinctive feature of the FreeStyle Router products is a smaller number of vias on the PCB with a smaller total length of conductors; in addition, the optimization of the placement of components is performed during the routing process. The preliminary version of the PCB design can be prepared using CAD-CAD and transferred to FreeStyle Router via PDIF format. The purchase of FreeStyle Router for DOS (price $950) entitles to purchase FreeStyle Suite with 50% discount.

- Диал Инжиниринг (2002-02-20). Уникальный трассировщик размещен на сайте [A unique router is available on the site] (in Russian). Archived from the original on 2017-09-26. Retrieved 2017-09-26.

- FreeStyle Router - топологический трассировщик (in Russian). 2003-09-30. Archived from the original on 2017-09-26. Retrieved 2017-09-26.

- ^ "News". ElekTrade. 2003-09-26. Archived from the original on 2003-12-05.

Today, the developers of the popular domestic autoroute program FreeStyleRoute announced the termination of the further development of its DOS version. In its place will come 32-bit Windows version of the program, called TopoR (TOPOlogical Router). The following changes are made to the version of TopoR 1.03 compared to FSR 1.6

- "Software Download". FreeStyleTeam. 2007. Archived from the original on 2007-11-13.

FreeStyleRoute V1.6 Topological PCB router for DOS. Freeware. 1.15 MB (1210820 bytes) 1.6 01.11.2003

- "FreeStyleRoute V1.6 Topological PCB router - Installation Guide". FreeStyleTeam. 2007. Archived from the original on 2007-11-16.

The FreeStyleRoute (FSR) program consists of a high-efficiency gridless two-layer PCB router SpeedWay and the FreeStyle editor. The editor can also be applied independently for routed boards corrections. It reaches the quality of routing and placement density, comparable or surpassing high-quality of manual routing. As a result, we have smooth wires, without breaks. The algorithms used in the design, allow to place any number of conductors between components pins. Compatible with P-CAD, by PDF-files. Version for DOS. Freeware. Now the program is not supported.

- Система топологической трассировки печатных плат TopoR ver 1.0 - Руководство пользователя [TopoR 1.0 Topological routing system - User manual] (PDF) (in Russian). St. Petersburg, Russia. 2003. Archived from the original (PDF) on 2005-01-16.

{{cite book}}: CS1 maint: location missing publisher (link) - ^ "Contacts". FreeStyleTeam. Archived from the original on 2007-11-13.

- "About group". FreeStyleTeam. 2007. Archived from the original on 2007-11-13.

- ЭлекТрейд (2006-01-17). Готовится к выходу новая версия трассировщика TopoR 3.0 [Preparing for release a new version of the router TopoR 3.0] (in Russian). Archived from the original on 2017-09-26. Retrieved 2017-09-26.

- "EDA Expert" (PDF). Chip-News (RU) (in Russian). 106 (3): 65–66. 2006. Archived (PDF) from the original on 2017-09-26. Retrieved 2017-09-26.

- "Version History". Eremex, Ltd. 2009. Archived from the original on 2009-03-06.

- Латышев, П. Н. (2011), Каталог САПР 2011—2012 Программы и производители [CAD Catalog 2011-2012 Programs and manufacturers] (in Russian), Moscow: Солон-Пресс, p. 600

- "TopoR Version History - What's New in TopoR version 6.2". Eremex. 2017-09-24. Archived from the original on 2017-09-24. Retrieved 2017-09-24. (NB. Includes a list of new features since TopoR 3.0. TopoR 5.4.14203 (2012-12-21) introduced support for EAGLE: "The Eagle BRD plain-text format is now supported. This format is used by files created in the Eagle 6.0 system.". Improved in TopoR 5.4.14362 (2013-07-02): "During import of Eagle BRD-files: in some cases the angle of rotation of pads was disregarded, in some cases the vias' pad size was assigned incorrectly, sometimes the wires on the inner layers were disappearing.")

- Uvarov , A. S. (2006). Проектирование печатных плат: 8 лучших программ [PCB design: The 8 best programs] (in Russian). ДМК Пресс . ISBN 5-94074-089-8.

- Карабран, В. М.; Зырин, И. Д. (2013). Методы снижения паразитной связи между проводниками [Methods for reducing the parasitic connection between conductors] (in Russian) (3). ТЭМС (TEMS): 68–77.

{{cite journal}}: Cite journal requires|journal=(help) - Лузин , Юрьевич Сергей ; Петросян , Геворг Самвелович ; Полубасов , Олег Борисович (2008). Проблемы трассировки печатных плат с BGA-компонентами [Problems of routing PCBs with BGA components] (PDF). Chip-News (in Russian). 2008 (5).

- Лузин , Юрьевич Сергей ; Петросян , Геворг Самвелович ; Полубасов , Олег Борисович (February 2009). "Probleme beim Routing von Leiterplatten mit BGA-Komponenten". Produktion von Leiterplatten und Systemen (in German). 2009 (2). Leuze-Verlag: 263–270.

- Лузин , Юрьевич Сергей ; Петросян , Геворг Самвелович ; Полубасов , Олег Борисович (November 2009). "Problems In Routing of PCB with BGA Components". OnBoard Technology. 2009 (11): 12–15. Archived from the original on 2012-04-26.

- Полубасов , Олег Борисович (2001) . "Глобальная минимизация количества межслой-ных переходов" [Global minimization of the number of interlayer junctions]. Технология и конструирование в электронной аппаратуре (TKEA) (in Russian). 2001 (2). НИИ "Звезда", St. Petersburg, Russia. УДК 681.14. Archived from the original on 2017-09-24. Retrieved 2017-09-24.

- ^ Blake, Anthony (2009-07-07) . "Topological Autorouter - Introduction". Archived from the original on 2011-02-27.

- Dayan, Tal (June 1997). Rubberband based topological router (PDF) (PhD thesis). University of California Santa Cruz. S2CID 107646249. Archived from the original (PDF) on 2017-07-18. Retrieved 2017-09-25 – via Semantic Scholar.

Further reading

- English

- Полубасов , Олег Борисович (May 2011). "Routing Concepts of a Topological Router CAD System". OnBoard Technology. 2011 (5): 11–15. Archived from the original on 2012-01-21.

- Lysenko , Andrew A. ; Лузин , Юрьевич Сергей ; Полубасов , Олег Борисович (September 2011). "Synchronizing Delays in Signal Transmission Lines". OnBoard Technology. 2011 (9): 14–17. Archived from the original on 2011-11-07.

- Popov, Sergei; Popov, Iurii (2013-12-05). "Speed and improve PCB routing". EDN Network. Archived from the original on 2017-09-24. Retrieved 2017-09-24.

- Russian

- Chip News:

- Полубасов , Олег Борисович (May 2002). Топологическая трассировка: реальность или миф? [Topological route: Reality or myth?] (PDF). Chip News / EDA Expert (in Russian). 68 (5): 42–46. Archived (PDF) from the original on 2017-10-03. Retrieved 2017-10-03.

- "Тоnор для радиоинженера" (PDF). Chip News / EDA Expert (in Russian). 77 (4): 73. April 2003. Archived (PDF) from the original on 2004-02-25. Retrieved 2017-10-03.

- #10, 2003

- Лузин , Юрьевич Сергей ; Полубасов , Олег Борисович (March 2006). "... TopoR" (PDF). Chip News / EDA Expert (in Russian). 106 (3): 74–76. Archived (PDF) from the original on 2017-09-27. Retrieved 2017-10-03.

- Electronics, #5, 2005

- Electronic components:

- Modern electronics journal:

- Потапов , Юрий (2002). ПОГОВОРИМ О ТРАССИРОВЩИКАХ [Talk about routers] (PDF) (3). ЭлекТрейд (ElekTrade): 1–3. Archived (PDF) from the original on 2021-04-22.

{{cite journal}}: Cite journal requires|journal=(help) (3 pages)

- German

- Лузин , Юрьевич Сергей ; Полубасов , Олег Борисович (September 2008). "Optimierung von Layouts mit TopoR". Produktion von Leiterplatten und Systemen (in German). 2008 (9). Leuze-Verlag: 1852–1856.

External links

- "Диал Инжиниринг" [Dial Engineering] (in Russian). 2002. Archived from the original on 2002-05-23. (Former website of Dial Engineering, developers of the FreeStyle Router up to 2002.)

- "FreeStyleTeam" (in Russian and English). 2009. Archived from the original on 2009-02-03. (Former website of the FreeStyleTeam, developers of FreeStyleRouter and TopoR up to 2009.)

- "Toporouter.com". 2013. Archived from the original on 2013-11-26. (Former 2009-2014 website for the TopoR router, as represented by Novarm, Ltd. and Eremex, Ltd. - unrelated to Anthony Blake's Toporouter.)

- "Eremex TopoR official site". (since 2008)

- "Eremex TopoR official site" (in Russian). (since 2008)

- "Eremex TopoR user forum". 2015-02-04.