Xeon Phi 5100 without heatsink Xeon Phi 5100 without heatsink | |

| General information | |

|---|---|

| Launched | 2010 |

| Discontinued | 2020 |

| Marketed by | Intel |

| Designed by | Intel |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 1.053 GHz to 1.7 GHz |

| Cache | |

| L1 cache | 32 KB per core |

| L2 cache | 512 KB per core |

| Architecture and classification | |

| Application | Supercomputers High-performance computing |

| Technology node | 45 nm transistors to 14 nm transistors (tri-gate) |

| Microarchitecture | Larrabee |

| Instruction set | x86-16 (except coprocessor form factor), IA-32, x86-64 |

| Extensions | |

| Physical specifications | |

| Cores |

|

| Memory (RAM) |

|

| Sockets | |

| Products, models, variants | |

| Core names |

|

| Model |

|

Xeon Phi is a discontinued series of x86 manycore processors designed and made by Intel. It was intended for use in supercomputers, servers, and high-end workstations. Its architecture allowed use of standard programming languages and application programming interfaces (APIs) such as OpenMP.

Xeon Phi launched in 2010. Since it was originally based on an earlier GPU design (codenamed "Larrabee") by Intel that was cancelled in 2009, it shared application areas with GPUs. The main difference between Xeon Phi and a GPGPU like Nvidia Tesla was that Xeon Phi, with an x86-compatible core, could, with less modification, run software that was originally targeted to a standard x86 CPU.

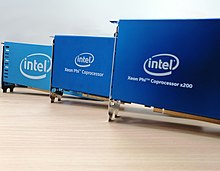

Initially in the form of PCI Express-based add-on cards, a second-generation product, codenamed Knights Landing, was announced in June 2013. These second-generation chips could be used as a standalone CPU, rather than just as an add-in card.

In June 2013, the Tianhe-2 supercomputer at the National Supercomputer Center in Guangzhou (NSCC-GZ) was announced as the world's fastest supercomputer (as of June 2023, it is No. 10). It used Intel Xeon Phi coprocessors and Ivy Bridge-EP Xeon E5 v2 processors to achieve 33.86 petaFLOPS.

The Xeon Phi product line directly competed with Nvidia's Tesla and AMD Radeon Instinct lines of deep learning and GPGPU cards. It was discontinued due to a lack of demand and Intel's problems with its 10nm node.

History

| Code name | Process | Comments |

|---|---|---|

| Knights Ferry | 45 nm | offered as PCI Express card; derived from Larrabee project |

| Knights Corner | 22 nm | derived from P54C; vector processing unit; first device to be announced as Xeon Phi; AVX-512-like encoding |

| Knights Landing | 14 nm | derived from Silvermont/Airmont (Intel Atom); AVX-512 |

| Knights Mill | 14 nm | nearly identical to Knights Landing but optimized for deep learning |

| Knights Hill | 10 nm | cancelled |

Background

The Larrabee microarchitecture (in development since 2006) introduced very wide (512-bit) SIMD units to an x86 architecture based processor design, extended to a cache-coherent multiprocessor system connected via a ring bus to memory; each core was capable of four-way multithreading. Due to the design being intended for GPU as well as general purpose computing, the Larrabee chips also included specialised hardware for texture sampling. The project to produce a retail GPU product directly from the Larrabee research project was terminated in May 2010.

Another contemporary Intel research project implementing x86 architecture on a many-multicore processor was the 'Single-chip Cloud Computer' (prototype introduced 2009), a design mimicking a cloud computing computer datacentre on a single chip with multiple independent cores: the prototype design included 48 cores per chip with hardware support for selective frequency and voltage control of cores to maximize energy efficiency, and incorporated a mesh network for inter-chip messaging. The design lacked cache-coherent cores and focused on principles that would allow the design to scale to many more cores.

The Teraflops Research Chip (prototype unveiled 2007) is an experimental 80-core chip with two floating-point units per core, implementing a 96-bit VLIW architecture instead of the x86 architecture. The project investigated intercore communication methods, per-chip power management, and achieved 1.01 TFLOPS at 3.16 GHz consuming 62 W of power.

Knights Ferry

Intel's Many Integrated Core (MIC) prototype board, named Knights Ferry, incorporating a processor codenamed Aubrey Isle was announced 31 May 2010. The product was stated to be a derivative of the Larrabee project and other Intel research including the Single-chip Cloud Computer.

The development product was offered as a PCIe card with 32 in-order cores at up to 1.2 GHz with four threads per core, 2 GB GDDR5 memory, and 8 MB coherent L2 cache (256 KB per core with 32 KB L1 cache), and a power requirement of ~300 W, built at a 45 nm process. In the Aubrey Isle core a 1,024-bit ring bus (512-bit bi-directional) connects processors to main memory. Single-board performance has exceeded 750 GFLOPS. The prototype boards only support single-precision floating-point instructions.

Initial developers included CERN, Korea Institute of Science and Technology Information (KISTI) and Leibniz Supercomputing Centre. Hardware vendors for prototype boards included IBM, SGI, HP, Dell and others.

Knights Corner

The Knights Corner product line is made at a 22 nm process size, using Intel's Tri-gate technology with more than 50 cores per chip, and is Intel's first many-cores commercial product.

In June 2011, SGI announced a partnership with Intel to use the MIC architecture in its high-performance computing products. In September 2011, it was announced that the Texas Advanced Computing Center (TACC) will use Knights Corner cards in their 10-petaFLOPS "Stampede" supercomputer, providing 8 petaFLOPS of compute power. According to "Stampede: A Comprehensive Petascale Computing Environment" the "second-generation Intel (Knights Landing) MICs will be added when they become available, increasing Stampede's aggregate peak performance to at least 15 PetaFLOPS."

On 15 November 2011, Intel showed an early silicon version of a Knights Corner processor.

On 5 June 2012, Intel released open source software and documentation regarding Knights Corner.

On 18 June 2012, Intel announced at the 2012 Hamburg International Supercomputing Conference that Xeon Phi will be the brand name used for all products based on their Many Integrated Core architecture. In June 2012, Cray announced it would be offering 22 nm 'Knight's Corner' chips (branded as 'Xeon Phi') as a co-processor in its 'Cascade' systems.

In June 2012, ScaleMP announced a virtualization update allowing Xeon Phi as a transparent processor extension, allowing legacy MMX/SSE code to run without code changes. An important component of the Intel Xeon Phi coprocessor's core is its vector processing unit (VPU). The VPU features a novel 512-bit SIMD instruction set, officially known as Intel Initial Many Core Instructions (Intel IMCI). Thus, the VPU can execute 16 single-precision (SP) or 8 double-precision (DP) operations per cycle. The VPU also supports Fused Multiply-Add (FMA) instructions and hence can execute 32 SP or 16 DP floating point operations per cycle. It also provides support for integers. The VPU also features an Extended Math Unit (EMU) that can execute operations such as reciprocal, square root, and logarithm, thereby allowing these operations to be executed in a vector fashion with high bandwidth. The EMU operates by calculating polynomial approximations of these functions.

On 12 November 2012, Intel announced two Xeon Phi coprocessor families using the 22 nm process size: the Xeon Phi 3100 and the Xeon Phi 5110P. The Xeon Phi 3100 will be capable of more than 1 teraFLOPS of double-precision floating-point instructions with 240 GB/s memory bandwidth at 300 W. The Xeon Phi 5110P will be capable of 1.01 teraFLOPS of double-precision floating-point instructions with 320 GB/s memory bandwidth at 225 W. The Xeon Phi 7120P will be capable of 1.2 teraFLOPS of double-precision floating-point instructions with 352 GB/s memory bandwidth at 300 W.

On 17 June 2013, the Tianhe-2 supercomputer was announced by TOP500 as the world's fastest. Tianhe-2 used Intel Ivy Bridge Xeon and Xeon Phi processors to achieve 33.86 petaFLOPS. It was the fastest on the list for two and a half years, lastly in November 2015.

Design and programming

The cores of Knights Corner are based on a modified version of P54C design, used in the original Pentium. The basis of the Intel MIC architecture is to leverage x86 legacy by creating an x86-compatible multiprocessor architecture that can use existing parallelization software tools. Programming tools include OpenMP, OpenCL, Cilk/Cilk Plus and specialised versions of Intel's Fortran, C++ and math libraries.

Design elements inherited from the Larrabee project include x86 ISA, 4-way SMT per core, 512-bit SIMD units, 32 KB L1 instruction cache, 32 KB L1 data cache, coherent L2 cache (512 KB per core), and ultra-wide ring bus connecting processors and memory.

The Knights Corner 512-bit SIMD instructions share many intrinsic functions with AVX-512 extension . The instruction set documentation is available from Intel under the extension name of KNC.

| Name | Serial Code | Cores (Threads @ 4× core) |

Clock (MHz) | L2 cache |

GDDR5 ECC memory | Peak DP compute (GFLOPS) |

TDP (W) |

Cooling system |

Form factor | Released | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Turbo | Quantity | Channels | BW GB/s | |||||||||

| Xeon Phi 3110X | SE3110X | 061 (244) | 1053 | – | 30.5 MB | 06 GB | 12 | 240 | 1028 | 300 | Bare board | PCIe 2.0 x16 card | November, 2012 |

| 08 GB | 16 | 320 | |||||||||||

| Xeon Phi 3120A | SC3120A | 057 (228) | 1100 | – | 28.5 MB | 06 GB | 12 | 240 | 1003 | 300 | Fan/heatsink | 17 June 2013 | |

| Xeon Phi 3120P | SC3120P | 057 (228) | 1100 | – | 28.5 MB | 06 GB | 12 | 240 | 1003 | 300 | Passive heatsink | 17 June 2013 | |

| Xeon Phi 31S1P | BC31S1P | 057 (228) | 1100 | – | 28.5 MB | 08 GB | 16 | 320 | 1003 | 270 | Passive heatsink | 17 June 2013 | |

| Xeon Phi 5110P | SC5110P | 060 (240) | 1053 | – | 30.0 MB | 08 GB | 16 | 320 | 1011 | 225 | Passive heatsink | 12 Nov 2012 | |

| Xeon Phi 5120D | SC5120D | 060 (240) | 1053 | - | 30.0 MB | 08 GB | 16 | 352 | 1011 | 245 | Bare board | SFF 230-pin card | 17 June 2013 |

| BC5120D | |||||||||||||

| Xeon Phi SE10P | SE10P | 061 (244) | 1100 | - | 30.5 MB | 08 GB | 16 | 352 | 1074 | 300 | Passive heatsink | PCIe 2.0 x16 card | 12 Nov. 2012 |

| Xeon Phi SE10X | SE10X | 061 (244) | 1100 | – | 30.5 MB | 08 GB | 16 | 352 | 1074 | 300 | Bare board | 12 Nov. 2012 | |

| Xeon Phi 7110P | SC7110P | 061 (244) | 1100 | 1250 | 30.5 MB | 16 GB | 16 | 352 | 1220 | 300 | Passive heatsink | ??? | |

| Xeon Phi 7110X | SC7110X | 061 (244) | 1250 | ??? | 30.5 MB | 16 GB | 16 | 352 | 1220 | 300 | Bare board | ??? | |

| Xeon Phi 7120A | SC7120A | 061 (244) | 1238 | 1333 | 30.5 MB | 16 GB | 16 | 352 | 1208 | 300 | Fan/heatsink | 6 April 2014 | |

| Xeon Phi 7120D | SC7120D | 061 (244) | 1238 | 1333 | 30.5 MB | 16 GB | 16 | 352 | 1208 | 270 | Bare board | SFF 230-pin card | March ??, 2014 |

| Xeon Phi 7120P | SC7120P | 061 (244) | 1238 | 1333 | 30.5 MB | 16 GB | 16 | 352 | 1208 | 300 | Passive heatsink | PCIe 2.0 x16 card | 17 June 2013 |

| Xeon Phi 7120X | SC7120X | 061 (244) | 1238 | 1333 | 30.5 MB | 16 GB | 16 | 352 | 1208 | 300 | Bare board | 17 June 2013 | |

Knights Landing

Code name for the second-generation MIC architecture product from Intel. Intel officially first revealed details of its second-generation Intel Xeon Phi products on 17 June 2013. Intel said that the next generation of Intel MIC Architecture-based products will be available in two forms, as a coprocessor or a host processor (CPU), and be manufactured using Intel's 14 nm process technology. Knights Landing products will include integrated on-package memory for significantly higher memory bandwidth.

Knights Landing contains up to 72 Airmont (Atom) cores with four threads per core, using LGA 3647 socket supporting up to 384 GB of "far" DDR4 2133 RAM and 8–16 GB of stacked "near" 3D MCDRAM, a version of the Hybrid Memory Cube. Each core has two 512-bit vector units and supports AVX-512 SIMD instructions, specifically the Intel AVX-512 Foundational Instructions (AVX-512F) with Intel AVX-512 Conflict Detection Instructions (AVX-512CD), Intel AVX-512 Exponential and Reciprocal Instructions (AVX-512ER), and Intel AVX-512 Prefetch Instructions (AVX-512PF). Support for IMCI has been removed in favor of AVX-512.

The National Energy Research Scientific Computing Center announced that Phase 2 of its newest supercomputing system "Cori" would use Knights Landing Xeon Phi coprocessors.

On 20 June 2016, Intel launched the Intel Xeon Phi product family x200 based on the Knights Landing architecture, stressing its applicability to not just traditional simulation workloads, but also to machine learning. The model lineup announced at launch included only Xeon Phi of bootable form-factor, but two versions of it: standard processors and processors with integrated Intel Omni-Path architecture fabric. The latter is denoted by the suffix F in the model number. Integrated fabric is expected to provide better latency at a lower cost than discrete high-performance network cards.

On 14 November 2016, the 48th list of TOP500 contained two systems using Knights Landing in the Top 10.

The PCIe based co-processor variant of Knight's Landing was never offered to the general market and was discontinued by August 2017. This included the 7220A, 7240P and 7220P coprocessor cards.

Intel announced they were discontinuing Knights Landing in summer 2018.

Models

All models can boost to their peak speeds, adding 200 MHz to their base frequency when running just one or two cores. When running from three to the maximum number of cores, the chips can only boost 100 MHz above the base frequency. All chips run high-AVX code at a frequency reduced by 200 MHz.

| Name | Serial Code | Cores (Threads @ 4× core) |

Clock (MHz) | L2 cache |

MCDRAM memory | DDR4 memory | TDP (W) |

Cooling system |

Form factor | Released | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Turbo | Quantity | BW | Capacity | BW | ||||||||

| Xeon Phi 7220A | SC7220A | 68 (272) | 1200 | 1400 | 34 MB | 16 GB | 400+ GB/s | 384 GB | 102.4 GB/s | 275 | Active heatsink | PCIe 3.0 x16 card | ??? |

| Xeon Phi 7220P | SC7220P | Passive heatsink | |||||||||||

| Xeon Phi 7240P | SC7240P | 1300 | 1500 | ||||||||||

| Xeon Phi 7200 Series |

sSpec number |

Cores (Threads) |

Clock (MHz) | L2 cache |

MCDRAM memory | DDR4 memory | Peak DP compute |

TDP (W) |

Socket | Release date | Part number | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Turbo | Quantity | BW | Capacity | BW | |||||||||

| Xeon Phi 7210 | SR2ME (B0) | 64 (256) | 1300 | 1500 | 32 MB | 16 GB | 400+ GB/s | 384 GB | 102.4 GB/s | 2662 GFLOPS |

215 | SVLCLGA3647 | 20 June 2016 | HJ8066702859300 |

| SR2X4 (B0) | ||||||||||||||

| Xeon Phi 7210F | SR2X5 (B0) | 230 | HJ8066702975000 | |||||||||||

| Xeon Phi 7230 | SR2MF (B0) | 215 | HJ8066702859400 | |||||||||||

| SR2X3 (B0) | ||||||||||||||

| Xeon Phi 7230F | SR2X2 (B0) | 230 | HJ8066702269002 | |||||||||||

| Xeon Phi 7250 | SR2MD (B0) | 68 (272) | 1400 | 1600 | 34 MB | 3046 GFLOPS |

215 | HJ8066702859200 | ||||||

| SR2X1 (B0) | ||||||||||||||

| Xeon Phi 7250F | SR2X0 (B0) | 230 | HJ8066702268900 | |||||||||||

| Xeon Phi 7290 | SR2WY (B0) | 72 (288) | 1500 | 1700 | 36 MB | 3456 GFLOPS |

245 | HJ8066702974700 | ||||||

| Xeon Phi 7290F | SR2WZ (B0) | 260 | HJ8066702975200 | |||||||||||

Knights Mill

Knights Mill is Intel's codename for a Xeon Phi product specialized in deep learning, initially released in December 2017. Nearly identical in specifications to Knights Landing, Knights Mill includes optimizations for better utilization of AVX-512 instructions. Single-precision and variable-precision floating-point performance increased, at the expense of double-precision floating-point performance.

- Models

| Xeon Phi 72x5 Series |

sSpec number |

Cores (Threads) |

Clock (MHz) | L2 cache |

MCDRAM memory | DDR4 memory | Peak DP compute |

TDP (W) |

Socket | Release date | Part number | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Turbo | Quantity | BW | Capacity | BW | |||||||||

| Xeon Phi 7235 | SR3VF (A0) | 64 (256) | 1300 | 1400 | 32 MB | 16 GB | 400+ GB/s | 384 GB | 102.4 GB/s | TBA | 250 | SVLCLGA3647 | Q4 2017 | HJ8068303823900 |

| Xeon Phi 7255 | SR3VG (A0) | 68 (272) | 1100 | 1200 | 34 MB | 115.2 GB/s | TBA | 215 | HJ8068303826300 | |||||

| Xeon Phi 7285 | SR3VE (A0) | 68 (272) | 1300 | 1400 | 34 MB | 115.2 GB/s | TBA | 250 | HJ8068303823800 | |||||

| Xeon Phi 7295 | SR3VD (A0) | 72 (288) | 1500 | 1600 | 36 MB | 115.2 GB/s | TBA | 320 | HJ8068303823700 | |||||

Knights Hill

Knights Hill was the codename for the third-generation MIC architecture, for which Intel announced the first details at SC14. It was to be manufactured in a 10 nm process.

Knights Hill was expected to be used in the United States Department of Energy Aurora supercomputer, to be deployed at Argonne National Laboratory. However, Aurora was delayed in favor of using an "advanced architecture" with a focus on machine learning.

In 2017, Intel announced that Knights Hill had been canceled in favor of another architecture built from the ground up to enable Exascale computing in the future. This new architecture is now expected for 2020–2021.

Programming

One performance and programmability study reported that achieving high performance with Xeon Phi still needs help from programmers and that merely relying on compilers with traditional programming models is insufficient. Other studies in various domains, such as life sciences and deep learning, have shown that exploiting the thread- and SIMD-parallelism of Xeon Phi achieves significant speed-ups.

Competitors

- Nvidia Tesla, a direct competitor in the HPC market

- AMD Radeon Pro and AMD Radeon Instinct direct competitors in the HPC market

See also

- Texas Advanced Computing Center – "Stampede" supercomputer incorporates Xeon Phi chips. Stampede is capable of 10 petaFLOPS.

- AVX-512

- Cell (microprocessor)

- Intel Tera-Scale

- Massively parallel

- Xeon

References

- Ian Cutress & Anton Shilov (7 May 2019). "The Larrabee Chapter Closes: Intel's Final Xeon Phi Processors Now in EOL". Retrieved 12 March 2020.

- "Intel® Xeon Phi™ Coprocessor System Software Developers Guide" (PDF). Intel. 8 November 2012. p. 16. Archived (PDF) from the original on 21 April 2024. Retrieved 1 May 2024.

- ^ Radek (18 June 2012). "Chip Shot: Intel Names the Technology to Revolutionize the Future of HPC - Intel Xeon Phi Product Family". Intel. Retrieved 12 December 2012.

- robert-reed (4 February 2013). "Best Known Methods for Using OpenMP on Intel Many Integrated Core (Intel MIC) Architecture". software.intel.com.

- Jeffers, James; Reinders, James (1 March 2013). Intel Xeon Phi Coprocessor High Performance Programming. Morgan Kaufmann. ISBN 978-0124104143.

- Hruska, Joel (8 May 2019). "Intel Quietly Kills Off Xeon Phi". ExtremeTech.

- "Intel scraps graphics chip based on Larrabee". Reuters. 6 December 2009.

- Sodani, Avinash; et al. (2016). "Knights Landing: Second-Generation Intel Xeon Phi Product". IEEE Micro. 36 (2): 34–46. doi:10.1109/MM.2016.25. S2CID 28837176.

- ^ "TOP500 - June 2013". TOP500. Retrieved 18 June 2013.

- "June 2023 | TOP500 Supercomputer Sites". www.top500.org.

- ^ "Intel Powers the World's Fastest Supercomputer, Reveals New and Future High Performance Computing Technologies". Retrieved 21 June 2013.

- W1zzard (24 July 2018). "Intel is Giving up on Xeon Phi - Eight More Models Declared End-Of-Life". TechPowerUp.

{{cite web}}: CS1 maint: numeric names: authors list (link) - Marc Sauter (20 June 2016). "Knights Landing: Intel veröffentlicht Xeon Phi mit bis zu 7 Teraflops - Golem.de". www.golem.de (in German).

- Charlie Demerjian (3 July 2006), "New from Intel: It's Mini-Cores!", theinquirer.net, The Inquirer, archived from the original on 29 August 2009

{{citation}}: CS1 maint: unfit URL (link) - Seiler, L.; Cavin, D.; Espasa, E.; Grochowski, T.; Juan, M.; Hanrahan, P.; Carmean, S.; Sprangle, A.; Forsyth, J.; Abrash, R.; Dubey, R.; Junkins, E.; Lake, T.; Sugerman, P. (August 2008). "Larrabee: A Many-Core x86 Architecture for Visual Computing" (PDF). ACM Transactions on Graphics. Proceedings of ACM SIGGRAPH 2008. 27 (3): 18:11. doi:10.1145/1360612.1360617. ISSN 0730-0301. S2CID 52799248. Archived from the original (PDF) on 10 September 2015. Retrieved 6 August 2008.

- Tom Forsyth, SIMD Programming with Larrabee (PDF), Intel

- Ryan Smith (25 May 2010), "Intel Kills Larrabee GPU, Will Not Bring a Discrete Graphics Product to Market\", www.anandtech.com, AnandTech

- Tony Bradley (3 December 2009), "Intel 48-Core "Single-Chip Cloud Computer" Improves Power Efficiency", pcworld.com, PCWorld

- "Intel Research : Single-Chip Cloud Computer", techresearch.intel.com, Intel

- Ben Ames (11 February 2007), "Intel Tests Chip Design With 80-Core Processor", pcworld.com, IDG News, archived from the original on 17 January 2012, retrieved 14 November 2018

- "Intel Details 80-Core Teraflops Research Chip - X-bit labs". xbitlabs.com. Archived from the original on 5 February 2015. Retrieved 27 August 2015.

- "Intel's Teraflops Research Chip" (PDF), download.intel.com, Intel, archived from the original (PDF) on 16 May 2021

- Anton Shilov (12 February 2007), "Intel Details 80-Core Teraflops Research Chip", xbitlabs.com, Xbit laboratories, archived from the original on 5 February 2015

- ^ Rupert Goodwins (1 June 2010), "Intel unveils many-core Knights platform for HPC", zdnet.co.uk, ZDNet

- "Intel News Release : Intel Unveils New Product Plans for High-Performance Computing", intel.com, Intel, 31 May 2010

- ^ Mike Giles (24 June 2010), "Runners and riders in GPU steeplechase" (PDF), people.maths.ox.ac.uk, pp. 8–10

- ^ Gareth Halfacree (20 June 2011), "Intel pushes for HPC space with Knights Corner", thinq.co.uk, Net Communities Limited, UK

- "Intel Many Integrated Core Architecture" (PDF), many-core.group.cam.ac.uk, Intel, December 2010, archived from the original (PDF) on 2 April 2012

- Rick Merritt (20 June 2011), "OEMs show systems with Intel MIC chips", EE Times

- Tom R. Halfhill (18 July 2011), "Intel Shows MIC Progress", linleygroup.com, The Linley Group

- Andrea Petrou (20 June 2011), "SGI wants Intel for super supercomputer", news.techeye.net, archived from the original on 16 September 2011

- ""Stampede's" Comprehensive Capabilities to Bolster U.S. Open Science Computational Resources" (Press release). Texas Advanced Computing Center. 22 September 2011. Archived from the original on 5 August 2012. Retrieved 23 September 2011.

- ^ "Stampede: A Comprehensive Petascale Computing Environment" (PDF). IEEE Cluster 2011 Special Topic. Archived from the original (PDF) on 26 September 2012. Retrieved 16 November 2011.

- Yam, Marcus (16 November 2011), "Intel's Knights Corner: 50+ Core 22nm Co-processor", tomshardware.com, Tom's Hardware, retrieved 16 November 2011

- Sylvie Barak (16 November 2011), "Intel unveils 1 TFLOP/s Knights Corner", EE Times, retrieved 16 November 2011

- James Reinders (5 June 2012), Knights Corner: Open source software stack, Intel

- Prickett Morgan, Timothy (18 June 2012), "Intel slaps Xeon Phi brand on MIC coprocessors", 222.theregister.co.uk

- Intel Corporation (18 June 2012), "Latest Intel Xeon Processors E5 Product Family Achieves Fastest Adoption of New Technology on Top500 List", marketwatch.com, archived from the original on 20 June 2012, retrieved 18 June 2012,

Intel Xeon Phi is the new brand name for all future Intel Many Integrated Core Architecture based products targeted at HPC, enterprise, datacenters and workstations. The first Intel Xeon Phi product family member is scheduled for volume production by the end of 2012

- Raj Hazra (18 June 2012). "Intel Xeon Phi coprocessors accelerate the pace of discovery and innovation". Intel. Retrieved 12 December 2012.

- Rick Merritt (18 June 2012). "Cray will use Intel MIC, branded Xeon Phi". EETimes. Retrieved 12 December 2012.

- Terrence O'Brien (18 June 2012). "Intel christens its 'Many Integrated Core' products Xeon Phi, eyes exascale milestone". Engadget. Retrieved 12 December 2012.

- Jeffrey Burt (18 June 2012). "Intel Wraps Xeon Phi Branding Around MIC Coprocessors". eWeek. Retrieved 7 March 2022.

- Merritt, Rick (8 June 2012), "Cray will use Intel MIC, branded Xeon Phi", eetimes.com

- Latif, Lawrence (19 June 2012), "Cray to support Intel's Xeon Phi in Cascade clusters", theinquirer.net, archived from the original on 22 June 2012

{{citation}}: CS1 maint: unfit URL (link) - "ScaleMP vSMP Foundation to Support Intel Xeon Phi" (Press release). ScaleMP. 20 June 2012. Archived from the original on 20 May 2013.

- George Chrysos (12 November 2012). "Intel Xeon Phi X100 Family Coprocessor - the Architecture". software.intel.com.

- ^ IntelPR (12 November 2012). "Intel Delivers New Architecture for Discovery with Intel Xeon Phi Coprocessors". Intel. Retrieved 12 December 2012.

- ^ Agam Shah (12 November 2012). "Intel ships 60-core Xeon Phi processor". Computerworld. Archived from the original on 12 March 2013. Retrieved 12 December 2012.

- ^ Johan De Gelas (14 November 2012). "The Xeon Phi at work at TACC". AnandTech. Retrieved 12 December 2012.

- "Tianhe-2 (MilkyWay-2)". Top500.org. 14 November 2015. Retrieved 6 May 2016.

- Hruska, Joel (30 July 2012). "Intel's 50-core champion: In-depth on Xeon Phi". ExtremeTech. Ziff Davis, Inc. Retrieved 2 December 2012.

- Barker, J; Bowden, J (2013). "Manycore Parallelism through OpenMP". OpenMP in the Era of Low Power Devices and Accelerators. IWOMP. Lecture Notes in Computer Science, vol 8122. Vol. 8122. Springer. pp. 45–57. doi:10.1007/978-3-642-40698-0_4. ISBN 978-3-642-40697-3.

- Rick Merritt (20 June 2011), "OEMs show systems with Intel MIC chips", EE Times

- Dokulil, Jiri; Bajrovic, Enes; Benkner, Siegfried; Pllana, Sabri; Sandrieser, Martin; Bachmayer, Beverly (23 November 2012), Efficient Hybrid Execution of C++ Applications using Intel Xeon Phi Coprocessor, arXiv:1211.5530, Bibcode:2012arXiv1211.5530D

- "News Fact Sheet: Intel Many Integrated Core (Intel MIC) Architecture ISC'11 Demos and Performance Description" (PDF), newsroom.intel.com, Intel, 20 June 2011, archived from the original (PDF) on 24 March 2012

- Tesla vs. Xeon Phi vs. Radeon. A Compiler Writer's Perspective // The Portland Group (PGI), CUG 2013 Proceedings

- "Intel Many Integrated Core Architecture (Intel MIC Architecture) - RESOURCES (including downloads)". Intel. Retrieved 6 January 2014.

- "Intel Xeon Phi Coprocessor Instruction Set Architecture Reference Manual" (PDF). Intel. 7 September 2012. Retrieved 6 January 2014.

- "Intel Developer Zone: Intel Xeon Phi Coprocessor". Intel. Archived from the original on 1 February 2014. Retrieved 6 January 2014.

- "Intel® Intrinsics Guide". software.intel.com. Retrieved 4 August 2020.

- "Intel SE3110X Xeon Phi 3110X Knights Corner 6GB Coprocessor-No Cooling -SabrePC.com -SabrePC.com". www.sabrepc.com. Archived from the original on 22 February 2017. Retrieved 22 February 2017.

- "Intel Xeon Phi Coprocessor 3120A (6GB, 1.100 GHz, 57 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Coprocessor 3120P (6GB, 1.100 GHz, 57 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi 31S1P - BC31S1P". www.cpu-world.com. Retrieved 21 April 2024.

- "Intel Xeon Phi Coprocessor 5110P (8GB, 1.053 GHz, 60 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Coprocessor 5120D (8GB, 1.053 GHz, 60 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi SE10P". www.cpu-world.com. Retrieved 21 April 2024.

- "Intel Xeon Phi SE10X". www.cpu-world.com. Retrieved 21 April 2024.

- "Intel SC7110P Xeon Phi 7110P Knights Corner Coprocessor -SabrePC.com -SabrePC.com". www.sabrepc.com. Retrieved 22 February 2017.

- "Intel SC7110X Xeon Phi 7110X Knights Corner Coprocessor -SabrePC.com -SabrePC.com". www.sabrepc.com. Retrieved 22 February 2017.

- "Intel Xeon Phi Coprocessor 7120A (16GB, 1.238 GHz, 61 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Coprocessor 7120D (16GB, 1.238 GHz, 61 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Coprocessor 7120P (16GB, 1.238 GHz, 61 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Coprocessor 7120X (16GB, 1.238 GHz, 61 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi 'Knights Landing' Features Integrated Memory With 500 GB/s Bandwidth and DDR4 Memory Support - Architecture Detailed". WCCFtech. 25 November 2013. Retrieved 27 August 2015.

- Sebastian Anthony (26 November 2013), Intel unveils 72-core x86 Knights Landing CPU for exascale supercomputing, ExtremeTech

- Tom's Hardware: Intel Xeon Phi Knights Landing Now Shipping; Omni Path Update, Too. 20 June 2016

- James Reinders (23 July 2013), AVX-512 Instructions, Intel

- "Cori". www.nersc.gov. Archived from the original on 17 May 2019. Retrieved 14 November 2018.

- ^ "2016 ISC High Performance: Intel's Rajeeb Hazra Delivers Keynote Address". Vimeo.

- Pradeep Dubey (20 June 2016). "How Intel Xeon Phi Processors Benefit Machine Learning/Deep Learning Apps and Frameworks". software.intel.com.

- "Introducing the Intel Xeon Phi Processor – Your Path to Deeper Insight". Intel. Archived from the original on 27 January 2017.

- "Highlights - November 2016 | TOP500". top500.org.

- Larabel, Michael (24 August 2017). "Intel Quietly Drops Xeon Phi 7200 Coprocessors". Phoronix. Retrieved 25 August 2017.

- "Product Change Notification 116378 - 00" (PDF). Intel.com. Retrieved 25 July 2018.

- "Intel Xeon Phi processor: Your Path to Deeper Insight" (PDF). Intel.com. Archived from the original (PDF) on 26 February 2017. Retrieved 25 February 2017.

- "Intel Xeon Phi 7220A - SC7220A / SC7220AEB".

- "Intel Xeon Phi 7220P - SC7220P".

- "Intel Xeon Phi 7240P - SC7240P".

- "Intel Xeon Phi Processor 7210 (16GB, 1.30 GHz, 64 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Processor 7210F (16GB, 1.30 GHz, 64 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Processor 7230 (16GB, 1.30 GHz, 64 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Processor 7230F (16GB, 1.30 GHz, 64 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Processor 7250 (16GB, 1.40 GHz, 68 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Processors". Intel. Retrieved 25 February 2017.

- "Intel Xeon Phi Processor 7250F (16GB, 1.40 GHz, 68 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Processor 7290 (16GB, 1.50 GHz, 72 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- "Intel Xeon Phi Processor 7290F (16GB, 1.50 GHz, 72 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- Smith, Ryan (17 August 2016). "Intel Announces Knight's Mill: A Xeon Phi for Deep Learning". Anandtech. Retrieved 17 August 2016.

- Cutress, Ian (19 December 2017). "Intel Lists Knights Mill Xeon Phi on ARK: Up to 72 cores at 320W with QFMA and VNNI". Anandtech. Retrieved 19 December 2017.

- SC14: Supercomputing '14; International Conference for High Performance Computing, Networking, Storage and Analysis in year 2014

- Eric Gardner (25 November 2014), What public disclosures has Intel made about Knights Landing?, Intel Corporation, archived from the original on 23 February 2015

- ALCF staff (9 April 2015), Introducing Aurora

- ALCF staff (9 April 2015), Aurora

- Hemsoth, Nicole (23 May 2017). "Some Surprises in the 2018 DoE Budget for Supercomputing". Next Platform. Retrieved 13 November 2017.

- Brueckner, Rich (16 June 2017). "Is Aurora Morphing into an Exascale AI Supercomputer?". Inside HPC. Retrieved 13 November 2017.

- Damkroger, Trish (13 November 2017). "Unleashing high performance computing today and tomorrow". Intel IT Peer Network.

- Kampman, Jeff (13 November 2017). "Intel quietly kills off next-gen Knights Hill Xeon Phi chips". Tech Report. Retrieved 13 November 2017.

- Fang, Jianbin; Sips, Henk; Zhang, Lilun; Xu, Chuanfu; Yonggang, Che; Varbanescu, Ana Lucia (2014). Test-Driving Intel Xeon Phi (PDF). 2014 ACM/SPEC International Conference on Performance Engineering. Archived from the original (PDF) on 11 November 2017. Retrieved 30 December 2013.

- Memeti, Suejb; Pllana, Sabri; Benkner, Siegfried; Pllana, Sabri; Sandrieser, Martin; Bachmayer, Beverly (29 June 2015), Accelerating DNA Sequence Analysis using Intel Xeon Phi, arXiv:1506.08612, Bibcode:2015arXiv150608612M

- Viebke, Andre; Pllana, Sabri; Benkner, Siegfried; Pllana, Sabri; Sandrieser, Martin; Bachmayer, Beverly (30 June 2015), The Potential of the Intel Xeon Phi for Supervised Deep Learning, arXiv:1506.09067, Bibcode:2015arXiv150609067V

- Jon Stokes (20 June 2011). "Intel takes wraps off 50-core supercomputing processor plans". Ars Technica.

- ^ Johan De Gelas (11 September 2012). "Intel's Xeon Phi in 10 Petaflops supercomputer". AnandTech. Retrieved 12 December 2012.

External links

- Intel pages: Intel Xeon Phi Processors

- Chips and Cheese, December 8, 2022, Knight's Landing: Atom with AVX-512

| Intel processors | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Lists | |||||||||||||||

| Microarchitectures |

| ||||||||||||||

| Current products |

| ||||||||||||||

| Discontinued |

| ||||||||||||||

| Related | |||||||||||||||