The PlayStation 2 technical specifications describe the various components of the PlayStation 2 (PS2) video game console.

Overview

The sixth-generation hardware of the PlayStation 2 video game console consists of various components. At the heart of the console's configuration is its central processing unit (CPU), a custom RISC processor known as the Emotion Engine which operates at 294.912 MHz (299 MHz in later consoles). The CPU heavily relies on its integration with two vector processing units, known as VPU0 and VPU1, the Graphics Synthesizer, and a floating-point unit (FPU) in order to render 3D graphics. Other components, such as the system's DVD-ROM optical drive and DualShock 2 controller, provide the software and user control input.

PlayStation 2 software is distributed on CD-ROM and DVD-ROM. In addition, the console can play audio CDs and DVD movies, and is backwards compatible with original PlayStation games. This is accomplished through the inclusion of the original PlayStation's CPU which also serves as the PS2's I/O processor, clocked at 36.864 MHz in PS2 mode. The PS2 also supports full functionality with the original PlayStation memory cards and controllers. The PS2's DualShock 2 controller is an upgraded version of the PlayStation's DualShock with analog face, shoulder and D-pad buttons replacing the digital buttons of the original. Like its predecessor, the DualShock 2 controller features force feedback technology.

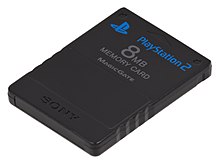

The standard PlayStation 2 memory card has an 8 MB capacity and uses Sony's MagicGate encryption. This requirement prevented the production of memory cards by third parties who did not purchase a MagicGate license. Memory cards without encryption can be used to store PlayStation game saves, but PlayStation games would be unable to read from or write to the card – such a card could only be used as a backup. There are a variety of non-Sony manufactured memory cards available for the PlayStation 2, allowing for a larger memory capacity than the standard 8 MB. However their use is unsupported and compatibility is not guaranteed. These memory cards can have up to 128 MB storage space.

The console also features USB and IEEE 1394 expansion ports. Compatibility with USB and IEEE 1394 devices is dependent on the software supporting the device. For example, the PS2 BIOS will not boot an ISO image from a USB flash drive or operate a USB printer, as the machine's operating system does not include this functionality. By contrast, Gran Turismo 4 and Tourist Trophy are programmed to save screenshots to a USB mass storage device and print images on certain USB printers. A PlayStation 2 HDD can be installed via the expansion bay in the back of the console, and was required to play certain games, notably the popular Final Fantasy XI.

Central processing unit

- CPU: MIPS III R5900-based "Emotion Engine", clocked at 294.912 MHz (299 MHz on newer versions), with 128-bit SIMD capabilities

- 250-nm CMOS manufacturing (ending with 65-nm CMOS), 13.5 million transistors, 225 mm² die size, 15 W dissipation (combined EE+GS in SCPH-7500x and later SCPH-7000x): 86 mm², 53.5 million transistors) (combined EE+GS+RDRAM+DRAM in SCPH-7900x ended with 65 nm CMOS design)

- CPU core: MIPS R5900 (COP0), 64-bit, little endian (mipsel). CPU is a superscalar, in-order execution 2-issue design with 6-stage long integer pipelines, 32 32-bit GPR registers, 32 128-bit SIMD linear scalar registers, two 64-bit integer ALUs, 128-bit load-store unit (LSU) and a branch execution unit (BXU).

- Instruction set: MIPS III, MIPS IV subset with Sony's proprietary 107 vector SIMD multimedia instructions (MMI). The custom instruction set was implemented by grouping the two 64-bit integer ALUs.

- 32-bit FPU coprocessor (COP1) with 6-stage long pipeline (floating point multiply accumulator × 1, floating point divider × 1). FPU is not IEEE compliant.

- Two 32-bit VLIW-SIMD vector units at 294.912 MHz: VPU0 and VPU1 (floating point multiply accumulator × 9, floating point divider × 1) each VPU contains a vector unit (VU), instruction cache, data cache and interface unit. Each vector unit also has upper execution unit containing 4 × FMAC and lower execution unit containing FDIV, integer ALU, load-store unit, branch logic, 16 16-bit integer registers and 32 128-bit floating point registers. VPU1 has an additional EFU unit.

- VPU0 (COP2; FMAC × 4, FDIV × 1) is tightly coupled with the main CPU and is typically used for polygon and geometry transformations (under parallel or serial connection), physics and other gameplay related tasks

- VPU1 (Elementary Functional Unit, EFU; FMAC × 5, FDIV × 2) operates independently controlled by microcode, parallel to the CPU core, is typically used for polygon and geometry transformations, clipping, culling, lighting and other visual based calculations (texture matrix includes processing of UV & STQ coordinates)

- Parallel: results of VU0/FPU sent as another display list via MFIFO (for e.g. complex characters/vehicles/etc.)

- Serial: results of VU0/FPU sent to VU1 (via 3 methods) and can act as an optional geometry pre-processor that does all base work to update the scene every frame (for e.g. general transformations of world space relating to gameplay, such as boning and animation, physics and general motion)

- Image Processing Unit (IPU): MPEG-2 compressed image macroblock layer decoder allowing playback of DVDs and game FMV. It also allowed vector quantization for 2D graphics data.

- Memory management unit (MMU), RDRAM controller and DMA controller: handle memory access within the system

- Cache memory: 16 KB instruction cache, 8 KB + 16 KB scratchpad (ScrP) data cache

- Scratchpad (SPR) is extended area of memory visible to the EE CPU. This extended memory provides 16 kilobytes of fast RAM available to be used by the application. Scratchpad memory can be used to store temporary data that is waiting to be sent via DMA or for any other temporary storage that the programmer can define.

Interfaces

- I/O processor interconnection: remote procedure call over a serial link, DMA controller for bulk transfer

- Main RDRAM memory bus. Bandwidth: 3.2 GB/s

- Graphics interface (GIF), DMA channel that connects the EE CPU to the GS ("Graphics Synthesizer") co-processor. To draw something to the screen, one must send, using 1 of 3 data paths, render commands & assets to the GS via the GIF channel: 64-bit, 150 MHz bus, maximum theoretical bandwidth of 1.2 GB/s.

- Display lists generated by CPU/VPU0 and VPU1 are sent to the GIF, which prioritizes them before dispatching them to the Graphics Synthesizer for rendering.

- Vector Unit Interface (VIF), consists of two DMA channels VIF0 for VPU0 and VIF1 for VPU1. Vector units and the main CPU communicate via VIF DMA channels.

- SIF – Serial Interface or Subsystem Interface which consists of 3 DMA channels:

- Subsystem Interface 0 (SIF0) and Subsystem Interface 1 (SIF1), used for communication between the EE main CPU and IOP co-processor. These are serial DMA channels where both CPUs can send commands and establish communication through an RPC protocol.

- Subsystem Interface 2 (SIF2), used for backwards compatibility with PS1 games and debugging.

Performance

- Floating point performance: 6.2 GFLOPS (single precision 32-bit floating point)

- FPU 0.64 GFLOPS

- VU0 2.44 GFLOPS

- VU1 3.08 GFLOPS (Including internal 0.64 GFLOPS EFU)

- Tri-strip geometric transformation (VU0+VU1): 150 million vertices per second

- 3D CG geometric transformation with raw 3D perspective operations (VU0+VU1): 66–80+ million vertices per second

- 3D CG geometric transformations at peak bones/movements/effects (textures)/lights (VU0+VU1, parallel or series): 15–20 million vertices per second

- Lighting: 38 million polygons/second

- Fog: 36 million polygons/second

- Curved surface generation (Bézier): 16 million polygons/second

- Image processing performance: 150 million pixels/second

- Actual real-world polygons (per frame): range of 500–600k at 30 FPS, 250–300k at 60 FPS

- Instructions per second: 6,000 MIPS (million instructions per second)

System memory

- Overall memory: 40 MB (42 MB after revision of system's IOP)

- Main memory: 32 MB PC800 32-bit dual-channel (2x 16-bit) RDRAM (Direct Rambus DRAM) @ 400 MHz, 3.2 GB/s peak bandwidth

- Stores all aspects & assets of an application or game's level, for fetching the right data at the right time, with assets being streamed to their appropriate destinations, when needed, a level's geometry, for instance, to either vector unit, via each unit's VIF, and textures to the GS, the system's GPU, via the GIF

- Video memory: 4 MB of 2560-bit DRAM @ 150 MHz, 48 GB/sec peak bandwidth

- Stores temporal work or drawing buffers for drawing operations & mapping procedures; main memory, again, pre-storing all aspects & assets of a level, streaming only what that part of the frame needs processed & drawn at a time to the GIF, accumulating a single frame in small, very quick doses, bit by bit, using the video memory's buffers & high bandwidth, along the transfer bus speeds provided

- IOP memory: 2 MB of 32-bit EDO-RAM @ 37.5 MHz, 150 MB/sec peak bandwidth

- Handles communication between external peripherals or devices & the hardware, also helping transfer data to the SPU2, the system's sound processing unit, via the same bus, its 32-bit bus being shared between the SPU2, optical drive, USB ports and more

- Updated to 4 MB SDRAM as of revision to SCPH-7500x model systems

- Sound memory: 2 MB of 32-bit EDO-RAM @ 37.5 MHz

- Separate memory that shares the same local 32-bit bus for the IOP, thus using from the same 150 Mb/sec bandwidth

- Main memory: 32 MB PC800 32-bit dual-channel (2x 16-bit) RDRAM (Direct Rambus DRAM) @ 400 MHz, 3.2 GB/s peak bandwidth

Graphics processing unit

- Parallel rendering processor with embedded DRAM "Graphics Synthesizer" (GS) clocked at 147.456 MHz

- 279 mm² die (combined EE+GS in SCPH-7500x: 86 mm², 53.5 million transistors)

- Dedicated connection from and to EE and VU1 via GIF

- Programmable CRT controller (PCRTC) for output

- Video output resolution: Variable from 256×224 to 1920×1080

- NTSC (interleaved/progressive scan): 256 x 448/224, 320 x 448/224, 384 x 448/224, 512 x 448/224 or 640 x 448/224

- PAL (interleaved/progressive scan): 256 x 512/256, 320 x 512/256, 384 x 512/256, 512 x 512/256 or 640 x 512/256

- VESA: 640 x 480, 800 x 600, 1024 x 768 or 1280×1024 pixels

- DTV: 720 x 480 (480p) or 1920 x 1080 (1080i)

- Video output resolution: Variable from 256×224 to 1920×1080

- 4 MB of embedded DRAM as video memory

- 48 gigabytes per second peak bandwidth

- Texture buffer bandwidth: 9.6 GB/s

- Frame buffer bandwidth: 38.4 GB/s

- 48 gigabytes per second peak bandwidth

- eDRAM bus width: 2560-bit (composed of three independent buses: 1024-bit write, 1024-bit read, 512-bit read/write)

- Pixel configuration: RGB:alpha, 24:8, 15:1; 16-, 24-, or 32-bit Z-buffer

- Display color depth: 32-bit (RGBA: 8 bits each)

- Pixel/Texel pipelines: 16 (unified)

- Raster setup & execution consists of the entire block of 16 pixel pipes being involved in every stage of drawing a frame, in parallel, being equipped to handle processing functions such as fogging, texture mapping, AA and more, cycles split between all pipes

- On their own, the 16 pipes output/process 16 pixels/cycle (1 pixel/pipe), giving a maximum throughput of 2400 megapixels/sec, at the GS's max clock speed, which includes 32bit pixels & all the systems basic alpha-blending, Z-buffering & filtering operations

- When needing to do texture mapping, the 16 pipes output/process 8 pixel/cycle & 8 texels/cycle, per each pipe, in parallel, for a maximum throughput of 1200 megapixels & 1200 megatexels

- The hardware's native fogging & AA uses additional cycles which reduces the overall throughput; but AA & fogging can be done as a post effect, using full-screen passes or sprites, and VRAM imaging operations, using then just a part of a said 2d vfx budget, as opposed to lowering the ceiling, perpetually, from the prior said textured fill-rate figure

- Raster setup & execution consists of the entire block of 16 pixel pipes being involved in every stage of drawing a frame, in parallel, being equipped to handle processing functions such as fogging, texture mapping, AA and more, cycles split between all pipes

- Overall pixel fillrate: 16 × 147 Mpix/s = 2.352 gigapixel/s

- 1.2 gigapixel/s (with Z-buffer, alpha, and texture)

- With no texture, flat shaded: 2.4 Gpix/s (75,000,000 32-pixel raster triangles)

- With 1 full texture (diffuse map), Gouraud shaded: 1.2 Gpix/s (37,750,000 32-bit pixel raster triangles)

- Texture fillrate: 1.2 Gtexel/s

- Sprite drawing rate: 18.75 million/s (8×8 pixels)

- Particle drawing rate: 150 million/s

- Polygon drawing rate: 75 million/s (small polygon)

- 50 million/s (48-pixel quad with Z and A)

- 30 million/s (50-pixel triangle with Z and A)

- 25 million/s (48-pixel quad with Z, A and T)

- 16 million/s (75-pixel triangle with Z, A, T and fog)

GS effects include: Dot3 bump mapping (normal mapping), mipmapping, spherical harmonic lighting, alpha blending, alpha test, destination alpha test, depth test, scissor test, transparency effects, framebuffer effects, post-processing effects, perspective-correct texture mapping, edge-AAx2 (poly sorting required), bilinear, trilinear texture filtering, multi-pass, palletizing (6:1 ratio 4-bit; 3:1 ratio 8-bit), offscreen drawing, framebuffer mask, flat shading, Gouraud shading, cel shading, dithering, texture swizzling.

- Multi-pass rendering ability

- Four passes: 300 Mpixel/s (75 Mpixels/pass)

Audio

- Audio: Sony SPU2 dual-core sound processing unit

- Local Memory: 2 MB EDO RAM (shared with the IOP)

- SPU Core(s): Two 16-bit Sony SPU cores clocked at 8 MHz (same as PS1)

- Supports ADPCM sources with up to 24 channels per core for a total of 48 channels

- Only one SPU core is used when in PS1 backwards compatibility mode

- One software-defined sound buffer source via PCM (primarily used for streaming audio)

- Sampling rates of up to 48 kHz or 44.1 kHz (selectable)

- Automatically downsampled to 44.1 kHz for PS1 backwards compatibility

- Supports applying digital effects for ADPCM sources

- Digital effects include:

- Pitch Modulation

- Envelope

- Looping

- Digital Reverb

- Digital effects include:

- Output: Gaussian interpolated output; stereo, Dolby Digital 5.1 Surround sound, DTS (Full motion video only), later games achieved matrix encoded 5.1 surround during gameplay through Dolby Pro Logic II

I/O processor (IOP)

- Input Output Processor (IOP)

- I/O Memory: 2 MB EDO DRAM

- CPU Core: Original PlayStation CPU (MIPS R3000A clocked at 33.8688 MHz or 36.864 MHz+PS1 GTE and MDEC for backwards compatibility with PS1 games)

- Automatically underclocked to 33.8688 MHz to achieve hardware backwards compatibility with original PlayStation format games.

- Sub Bus: 32-bit

- Connection to: SPU2 and CD/DVD controller.

- Replaced with the PowerPC-based "Deckard" IOP with 4 MB SDRAM starting with SCPH-7500x.

Storage

- Storage media:

- 8 MB memory card for saved games and data transfer

- Uses MagicGate encryption

- Read speeds of up to 130 KB/s

- Capacities of up to 128 MB or 256 MB (2x 128 MB) for some third-party memory cards

- Optional 40 GB hard disk drive (requires Network Adaptor)

- 8 MB memory card for saved games and data transfer

Optical disc drive

- Disc Drive type: proprietary interface through a custom micro-controller + DSP chip. 24x speed CD-ROM , 4x speed DVD-ROM — region-locked with copy protection.

- Supported Disc Media: PlayStation 2 format CD-ROM, PlayStation format CD-ROM, CD-DA, PlayStation 2 format DVD-ROM, DVD Video. DVD5 (Single-layer, 4.7 GB) and DVD9 (Dual-layer, 8.5 GB) supported. Later models starting with SCPH-500xx are DVD+RW and DVD-RW compatible.

Connectivity

PlayStation component (YPBPR) (left) and A/V (composite video/stereo audio) (right) cables

PlayStation component (YPBPR) (left) and A/V (composite video/stereo audio) (right) cables

- 2 proprietary PlayStation controller ports (250 kHz clock for PS1 and 500 kHz for PS2 controllers)

- 2 proprietary Memory Card slots using MagicGate encryption (250 kHz for PS1 cards. Up to 2 MHz for PS2 cards with an average sequential read speed of 130 KB/s)

- 2 USB 1.1 ports with an OHCI-compatible controller

- AV Multi Out (Composite video, S-Video, RGBS (SCART), RGsB (SCART or VGA connector), YPBPR (component or D-Terminal))

- RFU DC Out

- S/PDIF Digital Out

- Expansion Bay for 3.5-inch HDD and Network Adaptor (required for HDD, SCPH-300xx to 500xx only)

- PC Card slot for Network Adaptor (PC Card type) and External Hard Disk Drive (SCPH-10000, SCPH-15000, SCPH-18000 models)

- Emotion Engine (EE) includes an on-chip Serial I/O port (SIO) used internally by the EE's kernel to output debugging and messages and to start the kernel debugger.

- Ethernet port (Slim only)

- i.LINK S400 (also known as FireWire 400 or IEEE 1394a) (SCPH-10000 to 3900x only)

- Infrared remote control port (SCPH-500xx and newer)

^† Standard RGB mode only allows interlaced modes up to 480i (NTSC) and 576i (PAL) and progressive modes up to 240p. A display or adapter capable of sync on green (RGsB) is necessary for higher modes. Furthermore, the PS2's Macrovision copy protection isn't compatible with either RGB mode, and thus DVDs cannot be played with RGB. However, motherboard modifications have been known to bypass these issues.

^†† VGA connector is only available for progressive-scan supported games, homebrew-enabled systems, and Linux for PlayStation 2, and requires a monitor that supports RGsB, or "sync on green" signals.

^††† Contrary to popular belief, the PS2's YPBPR/component output does fully support 240p outputs, including games from the original PlayStation. However, 240p isn't part of the YPBPR standard, and thus not all TVs and HDTVs support it. Upscaling can be used as a workaround.

See also

- PlayStation technical specifications

- PlayStation 3 technical specifications

- PlayStation 4 technical specifications

References

- Stuart, Keith (12 December 2013). "PS4 and Xbox One: so why aren't they backwards compatible?". the Guardian. Archived from the original on 14 June 2015.

- "Dual Shock 2 Review". IGN. September 27, 2001. Archived from the original on 2011-05-15. Retrieved February 7, 2011.

The biggest difference between the Dual Shock 2 and the original… all of the buttons and even the digital pad offer analog support. This means that the d-pad, the four face buttons and the four shift buttons are all pressure-sensitive and have 255 degrees of sensitivity. It is also worth noting that the Dual Shock 2 is a bit lighter than the original Dual Shock because it appears to have less in the way of gears for the vibration function of the controller.

- "Final Fantasy XI Review for PlayStation 2 – GameSpot". Uk.gamespot.com. March 23, 2004. Archived from the original on July 21, 2011. Retrieved November 11, 2010.

- John L. Hennessy and David A. Patterson. "Computer Architecture: A Quantitative Approach, Third Edition". ISBN 1-55860-724-2

- Keith Diefendorff. "Sony's Emotionally Charged Chip". Microprocessor Report, Volume 13, Number 5, April 19, 1999. Microdesign Resources.

- ^ Hennessy, John L.; Patterson, David A. (29 May 2002). Computer Architecture: A Quantitative Approach (3 ed.). Morgan Kaufmann. ISBN 978-0-08-050252-6. Retrieved 9 April 2013.

- Sony Interactive Entertainmentsie.com Archived 2018-04-13 at the Wayback Machine

- "ソニー、65nm対応の半導体設備を導入。3年間で2,000億円の投資". pc.watch.impress.co.jp. Archived from the original on 2016-08-13.

- ^ "Tapping into the power of PS2" (PDF). Archived from the original (PDF) on July 20, 2011. Retrieved November 11, 2010. See bits on ps2's TnL & data setup. Also, look to pages 25 & 26 for a comparison of the ps2 to a PC architecture & memory setup, showing ps2 is based more around fast streaming of assets, as well as page 42 for a simple FSAA example.

- "Emotion". Kim L. Vu. Archived from the original on 14 June 2012. Retrieved 7 July 2011.

- "Aaron D Lanterman" (PDF). users.ece.gatech.edu. Archived (PDF) from the original on 2014-10-24.

- "Archived copy" (PDF). Archived (PDF) from the original on 2016-09-19. Retrieved 2016-02-07.

{{cite web}}: CS1 maint: archived copy as title (link) - "Vector Unit Architecture for Emotion Synthesis". Archived from the original on May 10, 2018. Retrieved April 26, 2017.

- "Designing and Programming the Emotion Engine" (PDF). Archived (PDF) from the original on April 28, 2017. Retrieved April 26, 2017.

- ^ "Inside the Playstation 2". philvaz.com. Archived from the original on March 4, 2011. Retrieved July 1, 2011.

- Malice PS2 Q&A See second question.

- ^ Amon Ra Prototype

- Coding Secrets/Game Hut See Coding Secrets video on PS2's poly count and particle effects.

- "Archived copy". Archived from the original on 2014-10-06. Retrieved 2014-09-30.

{{cite web}}: CS1 maint: archived copy as title (link) - Reaching for the Limits of PS2 Performance See pages 15 & 18, also, for an example of the default setup including sending textures, stored into main RAM at load up, to the GS, via the GIF.

- ^ PS2 Optimizations See pages 11-13 about texture syncing & transfer methods, an example of the PS2's setup. Also, see pg.29 for fill-rate for 4 passes, per second, likely at the standard PAL or NTSC rates of 50 Hz or 60 Hz, along with more evidence about using full-screen passes to implement bump mapping, with an example for alternative fogging being shown on pg.31.

- MDK2 Armageddon Chat Transcript "DavidBioWare What we've found since then is that the PS2 has enough bus bandwidth to transfer each texture from main memory to video memory as it's needed. That's on the order to 100s of Mb per second. We hadn't anticipated that the PS2 had that kind of brute horsepower on its bus. No other machine I've used does, including any PC or the Dreamcast. We had to reorient our thinking after that. :) So now we have almost more texture memory than we know what to do with."

- ^ Sony's Emotionally Charged Chip See pages 1, 2 & 4

- ^ PS2 Dev Wiki - IOP

- Introducing PS2 to PC programmers See pg.10 for IOP/SPU2 block

- PS2 Dev Wiki - SPU2

- "GS Mode Selector: Development & Feedback". psx-scene.com. Archived from the original on 2014-12-03.

- ^ GS User's Manual, Sony Computer Entertainment, 2001. See chapter/section 5.1.2 for ps2's output resolutions. Also, see chapter 1.2, specifically the diagram of pg.16 & "Pixel Pipeline" of pg.17, as well as chapter 3.1, namely Rasterizing (DDA) of pg.37, showing all the pixel pipes are involved in doing these operations, in parallel, including texture mapping. Lastly, look at pg.18 for GS performance figures.

- GS User's Manual Supplement. See chapter 1.4 about texturing via the DRAM & pixel engines.

- Using the Z Buffer for Visual and Special Effects

- "Archived copy" (PDF). Archived (PDF) from the original on 2015-05-16. Retrieved 2016-01-25.

{{cite web}}: CS1 maint: archived copy as title (link) - "Practical Implementation of SH Lighting and HDR Rendering". slidegur.com. Archived from the original on 2016-10-09.

- "Model numbers for PlayStation 2 and PS2 accessories". Archived from the original on 2010-03-16.

- "Model numbers for PlayStation 2 and PS2 accessories". Archived from the original on 2010-03-16.

- "PlayStation 2 SCPH-39001 Instruction manual". Archived from the original on 2013-12-16. Retrieved 2013-12-16.

- "SCEI Launches PlayStation 2 New Model SCPH-50000" (PDF). Archived from the original (PDF) on 2014-10-27. Retrieved 2013-12-16.

| PlayStation 2 | |

|---|---|

| Hardware | |

| Accessories | |

| Games | |

| Related | |

| |

| PlayStation | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Consoles |

| ||||||||||||||||||

| Games |

| ||||||||||||||||||

| Network | |||||||||||||||||||

| Accessories |

| ||||||||||||||||||

| Kits | |||||||||||||||||||

| Media |

| ||||||||||||||||||

| Arcade boards | |||||||||||||||||||

| Related | |||||||||||||||||||