In theoretical computer science, circuit complexity is a branch of computational complexity theory in which Boolean functions are classified according to the size or depth of the Boolean circuits that compute them. A related notion is the circuit complexity of a recursive language that is decided by a uniform family of circuits (see below).

Proving lower bounds on size of Boolean circuits computing explicit Boolean functions is a popular approach to separating complexity classes. For example, a prominent circuit class P/poly consists of Boolean functions computable by circuits of polynomial size. Proving that would separate P and NP (see below).

Complexity classes defined in terms of Boolean circuits include AC, AC, TC, NC, NC, and P/poly.

Size and depth

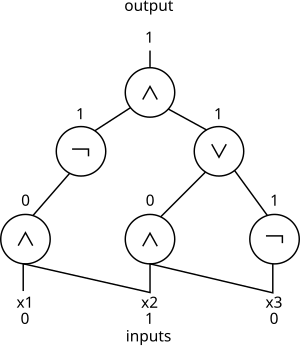

A Boolean circuit with input bits is a directed acyclic graph in which every node (usually called gates in this context) is either an input node of in-degree 0 labelled by one of the input bits, an AND gate, an OR gate, or a NOT gate. One of these gates is designated as the output gate. Such a circuit naturally computes a function of its inputs. The size of a circuit is the number of gates it contains and its depth is the maximal length of a path from an input gate to the output gate.

There are two major notions of circuit complexity The circuit-size complexity of a Boolean function is the minimal size of any circuit computing . The circuit-depth complexity of a Boolean function is the minimal depth of any circuit computing .

These notions generalize when one considers the circuit complexity of any language that contains strings with different bit lengths, especially infinite formal languages. Boolean circuits, however, only allow a fixed number of input bits. Thus, no single Boolean circuit is capable of deciding such a language. To account for this possibility, one considers families of circuits where each accepts inputs of size . Each circuit family will naturally generate the language by circuit outputting when a length string is a member of the family, and otherwise. We say that a family of circuits is size minimal if there is no other family that decides on inputs of any size, , with a circuit of smaller size than (respectively for depth minimal families). Thus, circuit complexity is meaningful even for non-recursive languages. The notion of a uniform family enables variants of circuit complexity to be related to algorithm based complexity measures of recursive languages. However, the non-uniform variant is helpful to find lower bounds on how complex any circuit family must be in order to decide given languages.

Hence, the circuit-size complexity of a formal language is defined as the function , that relates a bit length of an input, , to the circuit-size complexity of a minimal circuit that decides whether inputs of that length are in . The circuit-depth complexity is defined similarly.

Uniformity

Boolean circuits are one of the prime examples of so-called non-uniform models of computation in the sense that inputs of different lengths are processed by different circuits, in contrast with uniform models such as Turing machines where the same computational device is used for all possible input lengths. An individual computational problem is thus associated with a particular family of Boolean circuits where each is the circuit handling inputs of n bits. A uniformity condition is often imposed on these families, requiring the existence of some possibly resource-bounded Turing machine that, on input n, produces a description of the individual circuit . When this Turing machine has a running time polynomial in n, the circuit family is said to be P-uniform. The stricter requirement of DLOGTIME-uniformity is of particular interest in the study of shallow-depth circuit-classes such as AC or TC. When no resource bounds are specified, a language is recursive (i.e., decidable by a Turing machine) if and only if the language is decided by a uniform family of Boolean circuits.

Polynomial-time uniform

A family of Boolean circuits is polynomial-time uniform if there exists a deterministic Turing machine M, such that

- M runs in polynomial time

- For all , M outputs a description of on input

Logspace uniform

A family of Boolean circuits is logspace uniform if there exists a deterministic Turing machine M, such that

- M runs in logarithmic work space (i.e. M is a log-space transducer)

- For all , M outputs a description of on input

History

Circuit complexity goes back to Shannon in 1949, who proved that almost all Boolean functions on n variables require circuits of size Θ(2/n). Despite this fact, complexity theorists have so far been unable to prove a superlinear lower bound for any explicit function.

Superpolynomial lower bounds have been proved under certain restrictions on the family of circuits used. The first function for which superpolynomial circuit lower bounds were shown was the parity function, which computes the sum of its input bits modulo 2. The fact that parity is not contained in AC was first established independently by Ajtai in 1983 and by Furst, Saxe and Sipser in 1984. Later improvements by Håstad in 1987 established that any family of constant-depth circuits computing the parity function requires exponential size. Extending a result of Razborov, Smolensky in 1987 proved that this is true even if the circuit is augmented with gates computing the sum of its input bits modulo some odd prime p.

The k-clique problem is to decide whether a given graph on n vertices has a clique of size k. For any particular choice of the constants n and k, the graph can be encoded in binary using bits, which indicate for each possible edge whether it is present. Then the k-clique problem is formalized as a function such that outputs 1 if and only if the graph encoded by the string contains a clique of size k. This family of functions is monotone and can be computed by a family of circuits, but it has been shown that it cannot be computed by a polynomial-size family of monotone circuits (that is, circuits with AND and OR gates but without negation). The original result of Razborov in 1985 was later improved to an exponential-size lower bound by Alon and Boppana in 1987. In 2008, Rossman showed that constant-depth circuits with AND, OR, and NOT gates require size to solve the k-clique problem even in the average case. Moreover, there is a circuit of size that computes .

In 1999, Raz and McKenzie later showed that the monotone NC hierarchy is infinite.

The Integer Division Problem lies in uniform TC.

Circuit lower bounds

Circuit lower bounds are generally difficult. Known results include

- Parity is not in nonuniform AC, proved by Ajtai in 1983 as well as by Furst, Saxe and Sipser in 1984.

- Uniform TC is strictly contained in PP, proved by Allender.

- The classes S

2, PP and MA/1 (MA with one bit of advice) are not in SIZE(n) for any constant k. - While it is suspected that the nonuniform class ACC does not contain the majority function, it was only in 2010 that Williams proved that .

It is open whether NEXPTIME has nonuniform TC circuits.

Proofs of circuit lower bounds are strongly connected to derandomization. A proof that would imply that either or that permanent cannot be computed by nonuniform arithmetic circuits (polynomials) of polynomial size and polynomial degree.

In 1997, Razborov and Rudich showed that many known circuit lower bounds for explicit Boolean functions imply the existence of so called natural properties useful against the respective circuit class. On the other hand, natural properties useful against P/poly would break strong pseudorandom generators. This is often interpreted as a "natural proofs" barrier for proving strong circuit lower bounds. In 2016, Carmosino, Impagliazzo, Kabanets and Kolokolova proved that natural properties can be also used to construct efficient learning algorithms.

Complexity classes

| This section does not cite any sources. Please help improve this section by adding citations to reliable sources. Unsourced material may be challenged and removed. (October 2024) (Learn how and when to remove this message) |

Many circuit complexity classes are defined in terms of class hierarchies. For each non-negative integer i, there is a class NC, consisting of polynomial-size circuits of depth , using bounded fan-in AND, OR, and NOT gates. The union NC of all of these classes is a subject to discussion. By considering unbounded fan-in gates, the classes AC and AC (which is equal to NC) can be constructed. Many other circuit complexity classes with the same size and depth restrictions can be constructed by allowing different sets of gates.

Relation to time complexity

If a certain language, , belongs to the time-complexity class for some function , then has circuit complexity . If the Turing Machine that accepts the language is oblivious (meaning that it reads and writes the same memory cells regardless of input), then has circuit complexity .

Monotone circuits

A monotone Boolean circuit is one that has only AND and OR gates, but no NOT gates. A monotone circuit can only compute a monotone Boolean function, which is a function where for every , , where means that for all .

See also

Notes

- See proof.

References

- Sipser, Michael (1997). Introduction to the theory of computation (1 ed.). Boston, USA: PWS Publishing Company. p. 324.

- Shannon, Claude Elwood (1949). "The synthesis of two-terminal switching circuits". Bell System Technical Journal. 28 (1): 59–98. doi:10.1002/j.1538-7305.1949.tb03624.x.

- ^ Ajtai, Miklós (1983). "-formulae on finite structures". Annals of Pure and Applied Logic. 24: 1–24. doi:10.1016/0168-0072(83)90038-6.

- ^ Ajtai, Miklós; Komlós, János; Szemerédi, Endre (1983). "An sorting network". Proceedings of the 15th Annual ACM Symposium on Theory of Computing, 25–27 April, 1983, Boston, Massachusetts, USA. Association for Computing Machinery. pp. 1–9. doi:10.1145/800061.808726.

- ^ Furst, Merrick L.; Saxe, James Benjamin; Sipser, Michael Fredric (1984). "Parity, circuits, and the polynomial-time hierarchy". Mathematical Systems Theory. 17 (1): 13–27. doi:10.1007/BF01744431. MR 0738749. S2CID 6306235.

- Håstad, Johan Torkel (1987). Computational limitations of small depth circuits (PDF) (Ph.D. thesis). Massachusetts Institute of Technology.

- ^ Razborov, Aleksandr Aleksandrovich (1985). "Lower bounds on the monotone complexity of some Boolean functions". Soviet Mathematics - Doklady. 31: 354–357. ISSN 0197-6788.

- Smolensky, Roman (1987). "Algebraic methods in the theory of lower bounds for Boolean circuit complexity". Proceedings of the 19th Annual ACM Symposium on Theory of Computing. Association for Computing Machinery. pp. 77–82. doi:10.1145/28395.28404.

- Alon, Noga; Boppana, Ravi B. (1987). "The monotone circuit complexity of Boolean functions". Combinatorica. 7 (1): 1–22. CiteSeerX 10.1.1.300.9623. doi:10.1007/bf02579196. S2CID 17397273.

- Rossman, Benjamin E. (2008). "On the constant-depth complexity of k-clique". STOC 2008: Proceedings of the 40th annual ACM symposium on Theory of computing. Association for Computing Machinery. pp. 721–730. doi:10.1145/1374376.1374480.

- Raz, Ran; McKenzie, Pierre (1999). "Separation of the monotone NC hierarchy". Combinatorica. 19 (3): 403–435. doi:10.1007/s004930050062.

- Hesse, William (2001). "Division is in uniform TC". Proceedings of the 28th International Colloquium on Automata, Languages and Programming. Springer Verlag. pp. 104–114.

- Allender, Eric (1996). "Circuit complexity before the dawn of the new millennium". In Chandru, Vijay; Vinay, V. (eds.). Foundations of Software Technology and Theoretical Computer Science, 16th Conference, Hyderabad, India, December 18–20, 1996, Proceedings. Lecture Notes in Computer Science. Vol. 1180. Springer. pp. 1–18. doi:10.1007/3-540-62034-6_33.

- Santhanam, Rahul (2007). "Circuit lower bounds for Merlin-Arthur classes". STOC 2007: Proceedings of the thirty-ninth annual ACM symposium on Theory of computing. pp. 275–283. CiteSeerX 10.1.1.92.4422. doi:10.1145/1250790.1250832.

- Williams, Richard Ryan (2011). "Non-Uniform ACC Circuit Lower Bounds" (PDF). CCC 2011: Proceedings of the 26th Annual IEEE Conference on Computational Complexity. pp. 115–125. doi:10.1109/CCC.2011.36.

- Kabanets, Valentine; Impagliazzo, Russell Graham (2004). "Derandomizing polynomial identity tests means proving circuit lower bounds". Computational Complexity. 13 (1): 1–46. doi:10.1007/s00037-004-0182-6. S2CID 12451799.

- Razborov, Aleksandr Aleksandrovich; Rudich, Steven (1997). "Natural proofs". Journal of Computer and System Sciences. Vol. 55. pp. 24–35.

- Carmosino, Marco; Impagliazzo, Russell Graham; Kabanets, Valentine; Kolokolova, Antonina (2016). "Learning algorithms from natural proofs". Computational Complexity Conference.

- Pippenger, Nicholas; Fischer, Michael J. (1979). "Relations Among Complexity Measures". Journal of the ACM. 26 (3): 361–381. doi:10.1145/322123.322138. S2CID 2432526.

Further reading

- Vollmer, Heribert (1999). Introduction to Circuit Complexity: a Uniform Approach. Texts in Theoretical Computer Science. An EATCS Series. Springer Verlag. ISBN 978-3-540-64310-4.

- Wegener, Ingo (1987) . The Complexity of Boolean Functions. Wiley–Teubner Series in Computer Sciences. Frankfurt am Main/Bielefeld, Germany: John Wiley & Sons Ltd., and B. G. Teubner Verlag, Stuttgart. ISBN 3-519-02107-2. LCCN 87-10388. (xii+457 pages) (NB. At the time an influential textbook on the subject, commonly known as the "Blue Book". Also available for download (PDF) at the Electronic Colloquium on Computational Complexity.)

- Zwick, Uri. "Lecture notes for a course of Uri Zwick on circuit complexity".

nodes are

nodes are  nodes are

nodes are  nodes are

nodes are  (see below).

(see below).

would separate

would separate  input

input  is the minimal size of any circuit computing

is the minimal size of any circuit computing  accepts inputs of size

accepts inputs of size  when a length

when a length  otherwise. We say that a family of circuits is size minimal if there is no other family that decides on inputs of any size,

otherwise. We say that a family of circuits is size minimal if there is no other family that decides on inputs of any size,  is defined as the function

is defined as the function  , that relates a bit length of an input,

, that relates a bit length of an input,  where each

where each  is polynomial-time uniform if there exists a

is polynomial-time uniform if there exists a  , M outputs a description of

, M outputs a description of

bits, which indicate for each possible edge whether it is present. Then the k-clique problem is formalized as a function

bits, which indicate for each possible edge whether it is present. Then the k-clique problem is formalized as a function  such that

such that  outputs 1 if and only if the graph encoded by the string contains a clique of size k. This family of functions is monotone and can be computed by a family of circuits, but it has been shown that it cannot be computed by a polynomial-size family of monotone circuits (that is, circuits with AND and OR gates but without negation). The original result of

outputs 1 if and only if the graph encoded by the string contains a clique of size k. This family of functions is monotone and can be computed by a family of circuits, but it has been shown that it cannot be computed by a polynomial-size family of monotone circuits (that is, circuits with AND and OR gates but without negation). The original result of  to solve the k-clique problem even in the

to solve the k-clique problem even in the  that computes

that computes  .

. would imply that either

would imply that either  or that permanent cannot be computed by nonuniform arithmetic circuits (polynomials) of polynomial size and polynomial degree.

or that permanent cannot be computed by nonuniform arithmetic circuits (polynomials) of polynomial size and polynomial degree.

, using bounded

, using bounded  for some function

for some function  . If the Turing Machine that accepts the language is

. If the Turing Machine that accepts the language is  .

.

where for every

where for every  ,

,  , where

, where  means that

means that  for all

for all  .

.

-formulae on finite structures". Annals of Pure and Applied Logic. 24: 1–24.

-formulae on finite structures". Annals of Pure and Applied Logic. 24: 1–24.  sorting network". Proceedings of the 15th Annual ACM Symposium on Theory of Computing, 25–27 April, 1983, Boston, Massachusetts, USA. Association for Computing Machinery. pp. 1–9.

sorting network". Proceedings of the 15th Annual ACM Symposium on Theory of Computing, 25–27 April, 1983, Boston, Massachusetts, USA. Association for Computing Machinery. pp. 1–9.